# COMPUTER ARCHITECTURE AND ORGANIZATION.

### **UNIT-1**

Presented by Dr.K.RAJKAMAL, Assoc.Prof, Dept of ECE, KHIT.

|                  |  |                                                 | L | T | P | Cr. |

|------------------|--|-------------------------------------------------|---|---|---|-----|

| B.Tech. (5_Sem.) |  | COMPUTER ARCHITECTURE AND ORGANIZATION (Theory) | 3 | 0 | 0 | 3   |

|                  |  |                                                 |   |   |   |     |

Pre-requisites: Digital Logic Design

#### Course Educational Objective:

- 1. To understand the architecture of a modern computer with its various processing units. Also the Performance measurement of the computer system.

- 2. To understand the memory management system of computer.

- 3. To understand the various instructions, addressing modes

- 4. To understand the concept of I/O organization

#### **Course Outcomes:**

At the end of the course, the student will be able to

CO1: Understand the architecture of modern computer.

CO2: Analyze the Performance of a computer using performance equation

CO3: Understanding of different instruction types.

CO4: Calculate the effective address of an operand by addressing modes

CO5: Understand the concepts of I/O Organization and Memory systems.

#### UNIT - I

Basic Structure Of Computers: Functional unit, Basic Operational concepts, Bus structures, System Software, Performance, The history of computer development.

#### Machine Instruction and Programs:

Instruction and Instruction Sequencing: Register Transfer Notation, Assembly Language Notation, Basic Instruction Types,

#### UNIT - II

Addressing Modes, Basic Input/output Operations, The role of Stacks and Queues in computer programming equation. Component of Instructions: Logic Instructions, shift and Rotate Instructions

Type of Instructions: Arithmetic and Logic Instructions, Branch Instructions, Addressing Modes, Input/output Operations

#### UNIT - III

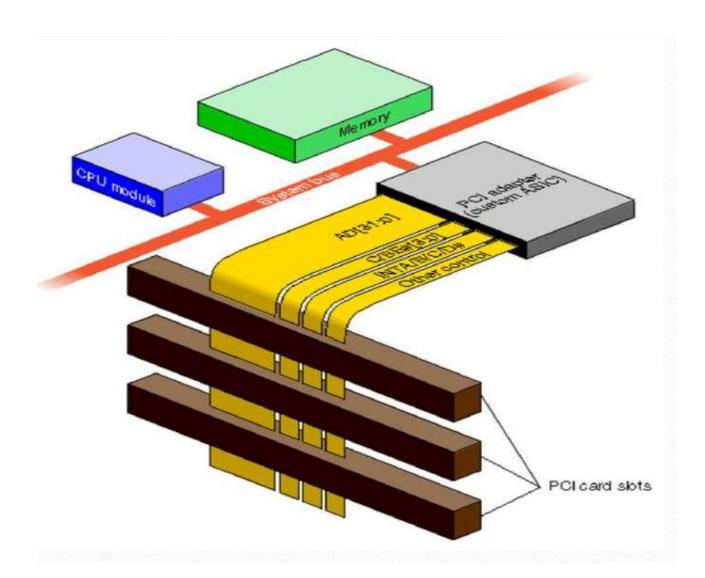

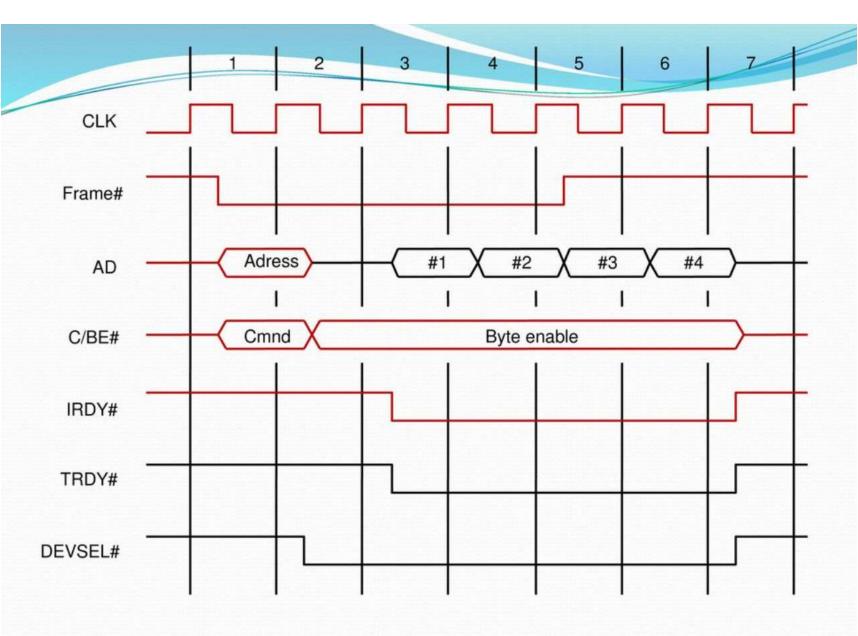

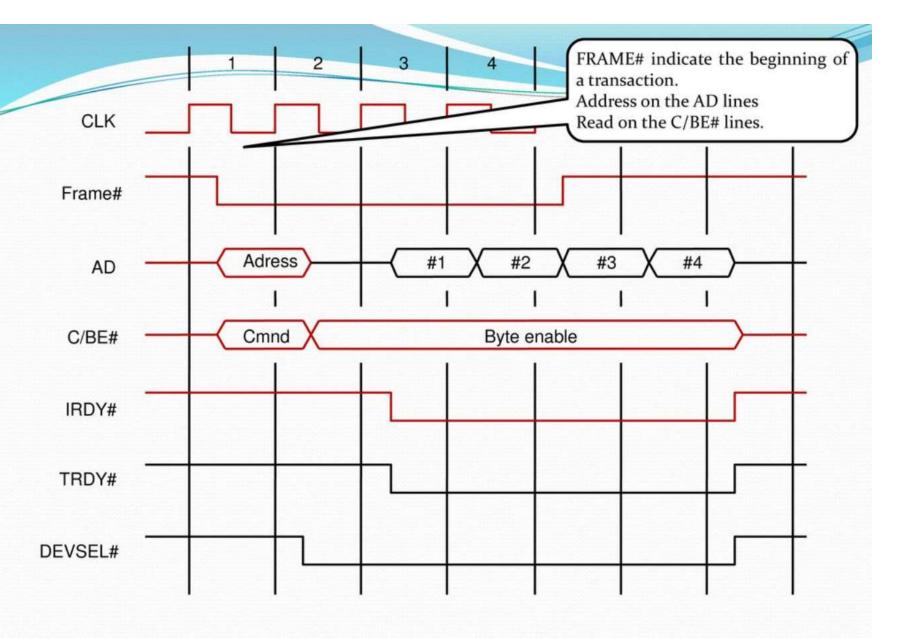

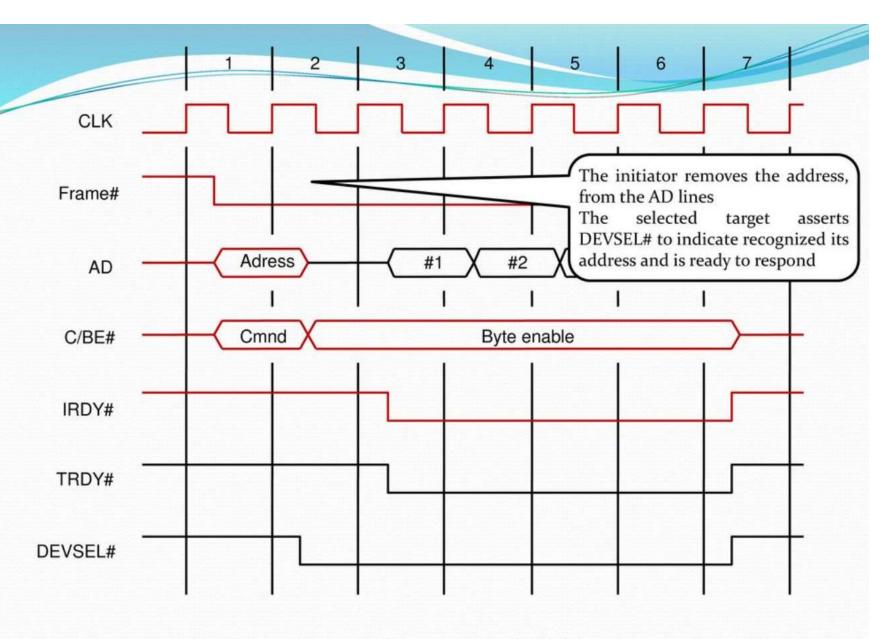

INPUT/OUTPUT ORGANIZATION: Accessing I/O Devices, Interrupts: Interrupt Hardware, Enabling and Disabling Interrupts, Handling Multiple Devices, Direct Memory Access, Buses: Synchronous Bus, Asynchronous Bus, Interface Circuits, Standard I/O Interface: Peripheral Component Interconnect (PCI) Bus, Universal Serial Bus (USB)

#### UNIT - IV

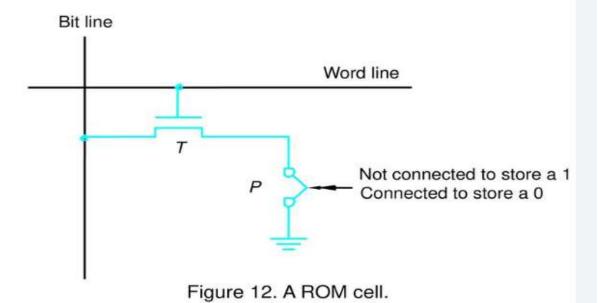

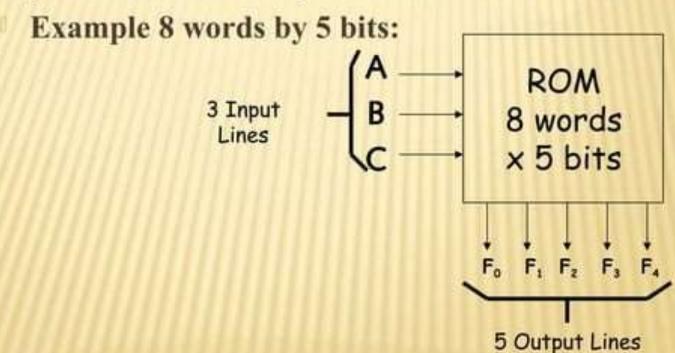

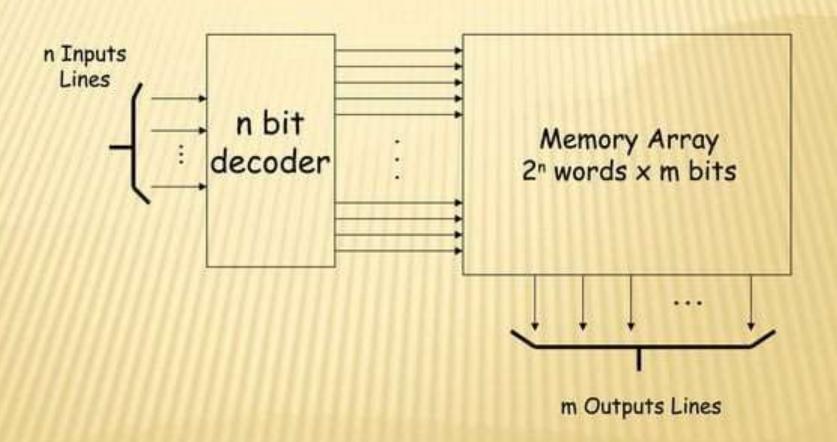

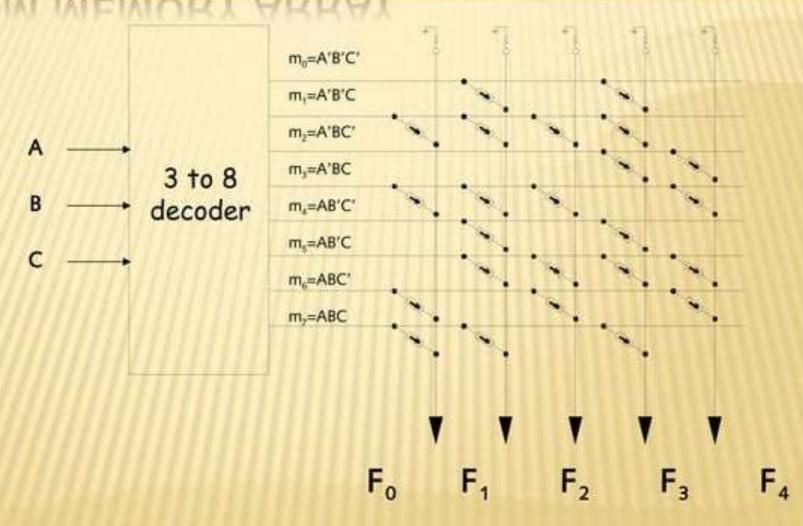

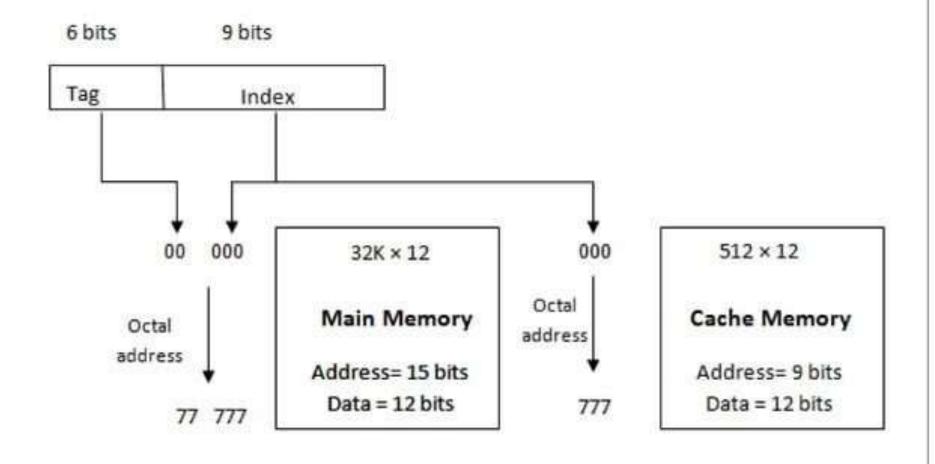

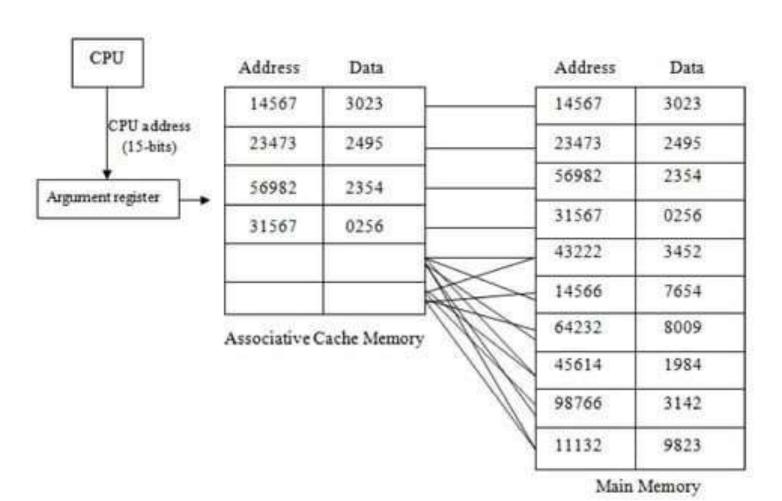

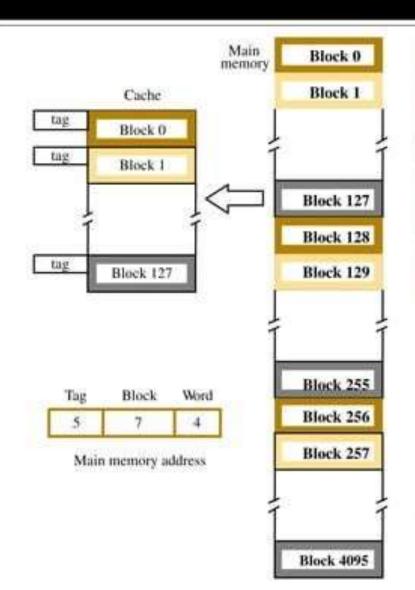

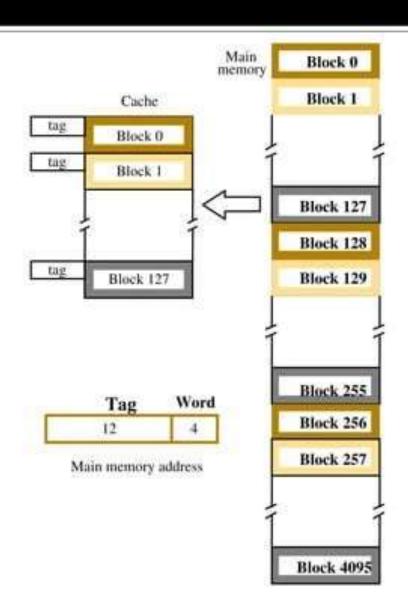

The MEMORY SYSTEMS: Basic memory circuits, Memory System Consideration, Read-Only Memory: ROM, PROM, EPROM, EEPROM, Flash Memory, Introduction about Cache Memories

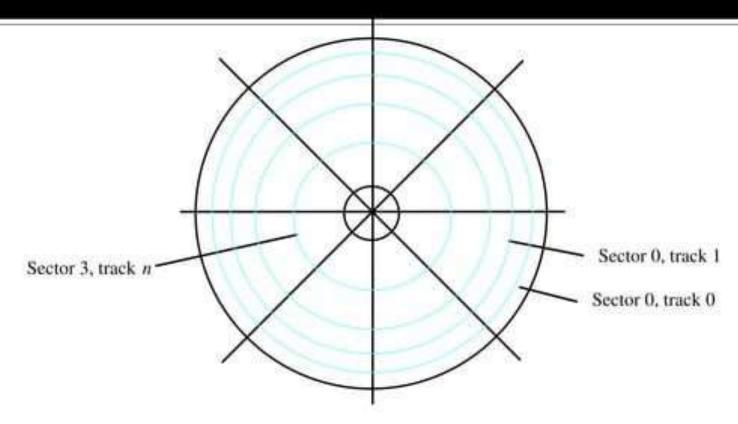

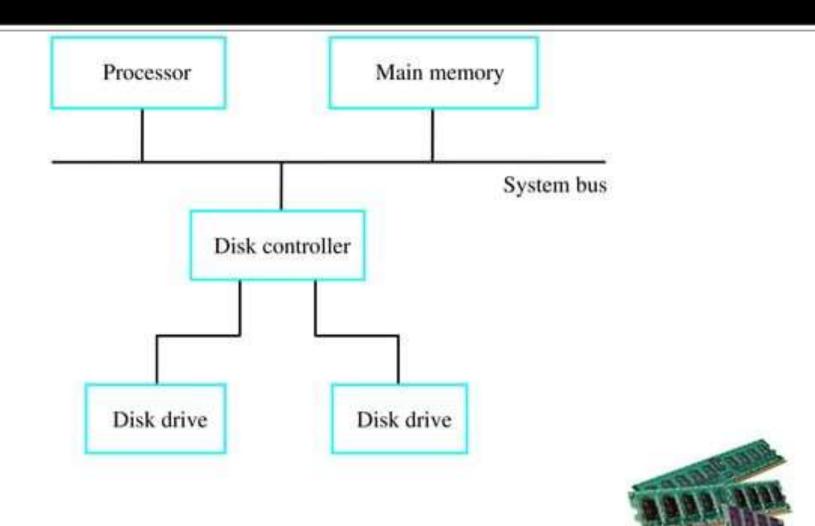

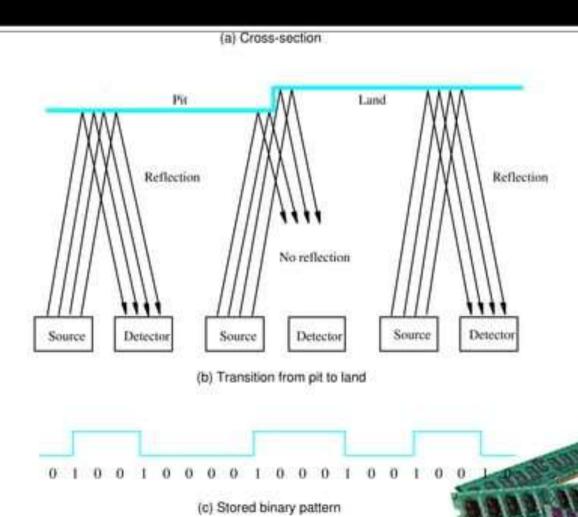

Secondary Storage: Magnetic Hard Disks, Optical Disks,

#### UNIT - V

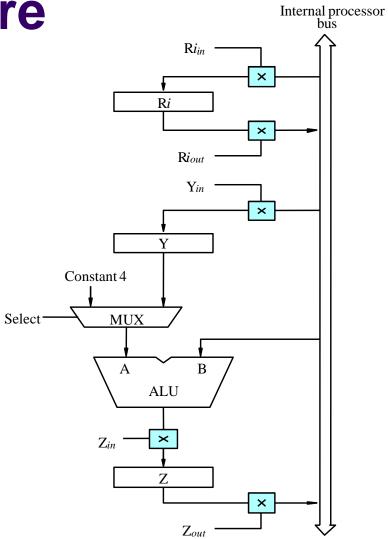

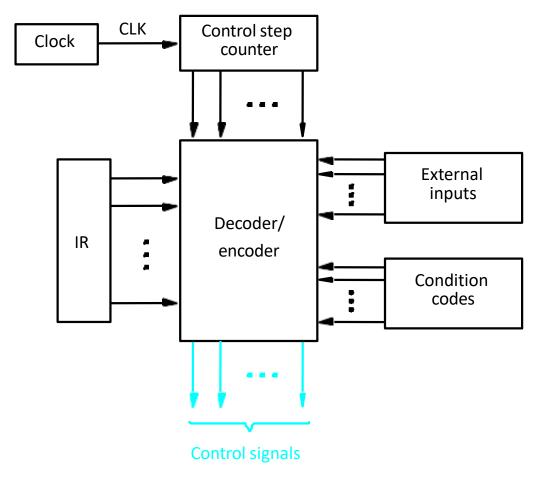

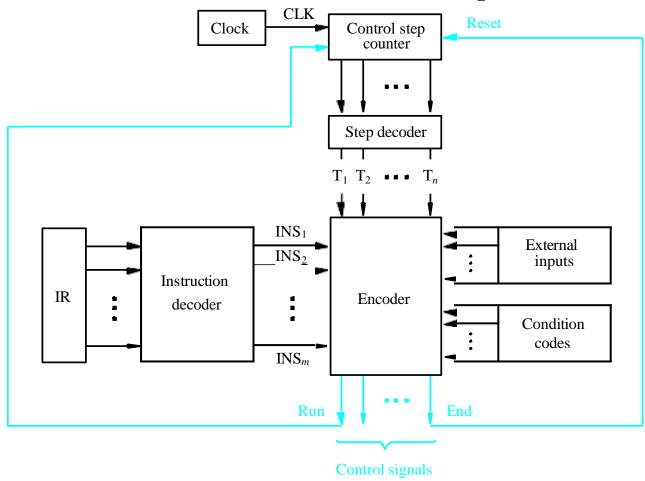

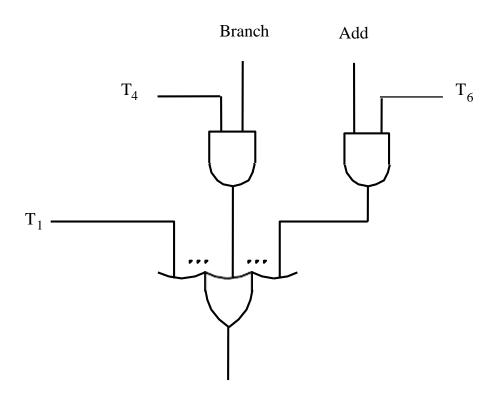

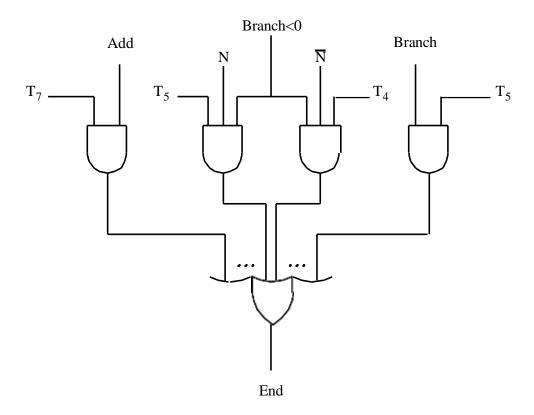

Processing Unit: Fundamental Concepts: Register Transfers, Performing an Arithmetic Or Logic Operation, Fetching a Word from Memory, Execution of Complete Instruction, Hardwired Control,

#### TEXT BOOKS

- Computer Organization, Carl Hamacher, ZvonksVranesic, SafeaZaky, 5thEdition, McGrawHill, 2011.

- 2. Computer Architecture and Organization, John P. Hayes, 3rd Edition, McGrawHill, 2002.

#### REFERENCE

- 1. Computer Organization and Architecture William Stallings Sixth Edition, Pearson/PHI

- 2. Structured Computer Organization Andrew S. Tanenbaum, 4th Edition PHI/Pearson, 2012.

- 3. Fundamentals or Computer Organization and Design, Sivaraama Dandamudi Springer Int.Edition, 2003.

- 4. "Computer Organization and Design: The Hardware/Software Interface" by David A. Patterson and John L.Hennessy, 1998.

- 5. J.P. Hayes, "Computer Architecture and Organization", McGraw-Hill, 1998.

# Architecture

- Structure and behavior of the computer as seen by the user.

- those properties, which directly affect the logical working of a program;

- the attributes, which are apparent to a programmer

Examples: instruction set and formats, techniques for addressing memory, number of bits used to represent data

# Organization

- Organization: interconnection of operational units for realizing the architectural specifications

- Determination of which hardware should be used and

- how the parts should be connected together

### BASIC STRUCTURE OF COMPUTERS

# > Functional Units

# **Functional Units**

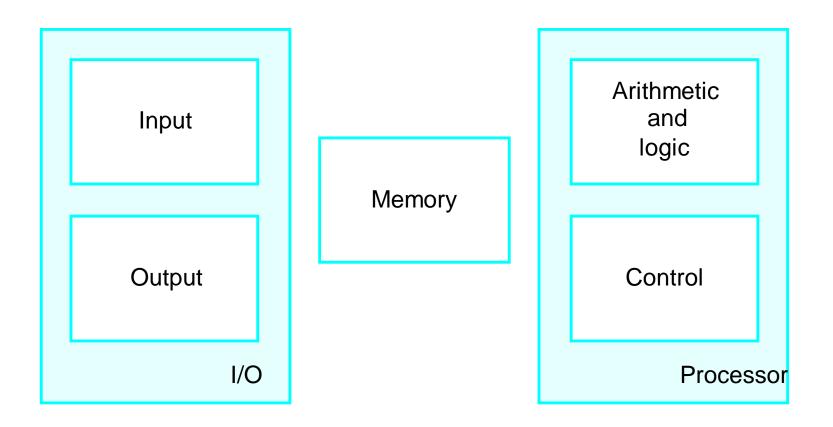

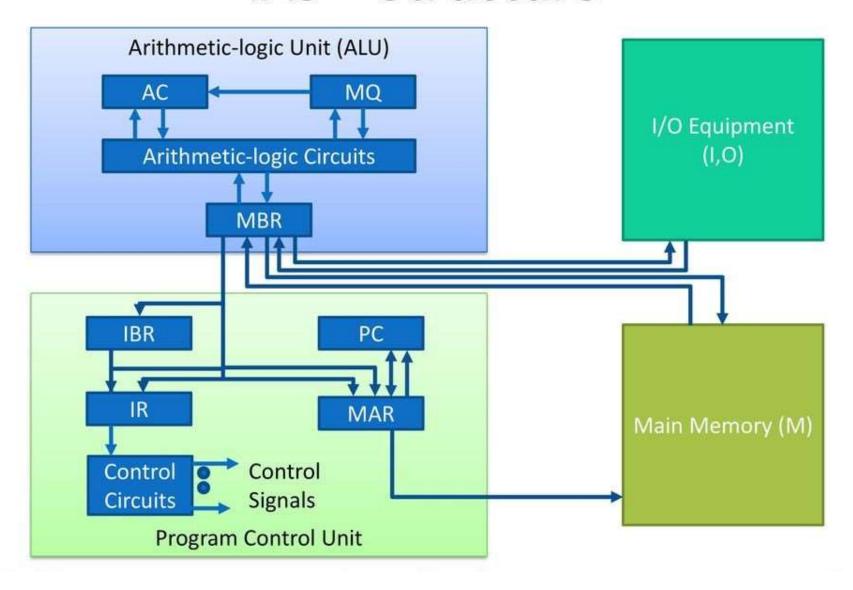

Figure 1.1. Basic functional units of a computer.

# Information Handled by a Computer

- Instructions/machine instructions

- ➤ Govern the transfer of information within a computer as well as between the computer and its I/O devices

- Specify the arithmetic and logic operations to be performed

- > Program

- Data

- Used as operands by the instructions

- Source program

- Encoded in binary code 0 and 1

# **Memory Unit**

- Store programs and data

- Two classes of storage

- Primary storage

- Fast

- Programs must be stored in memory while they are being executed

- ❖ Large number of semiconductor storage cells

- Processed in words

- Address

- RAM and memory access time

- Memory hierarchy cache, main memory

- Secondary storage larger and cheaper

# Arithmetic and Logic Unit (ALU)

- Most computer operations are executed in ALU of the processor.

- Load the operands into memory bring them to the processor – perform operation in ALU – store the result back to memory or retain in the processor.

- Registers

- Fast control of ALU

# **Control Unit**

- All computer operations are controlled by the control unit.

- The timing signals that govern the I/O transfers are also generated by the control unit.

- Control unit is usually distributed throughout the machine instead of standing alone.

- Operations of a computer:

- Accept information in the form of programs and data through an input unit and store it in the memory

- Fetch the information stored in the memory, under program control, into an ALU, where the information is processed

- Output the processed information through an output unit

- > Control all activities inside the machine through a control unit

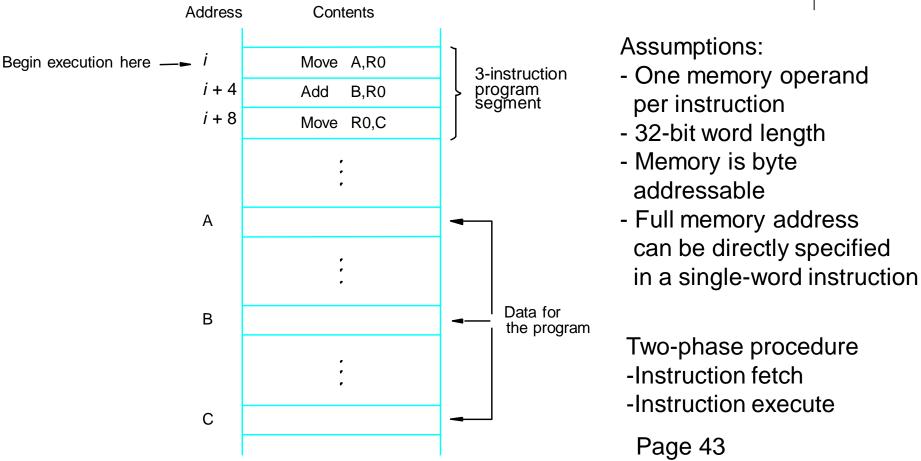

To perform a given task an appropriate program consisting of a list of instructions is stored in the memory. Individual instructions are brought from the memory into the processor, which executes the specified operations. Data to be stored are also stored in the memory.

### Examples: - Add LOCA, R0

- → This instruction adds the operand at memory location LOCA, to operand in register R0 & places the sum into register. This instruction requires the performance of several steps,

- 1. First the instruction is fetched from the memory into the processor.

- 2. The operand at LOCA is fetched and added to the contents of R0

- 3. Finally the resulting sum is stored in the register R0

# COMPUTER

→ The preceding add instruction combines a memory access operation with an ALU Operations. In some other type of computers, these two types of operations are performed by separate instructions for performance reasons.

Load LOCA, R1 Add R1, R0

→ Transfers between the memory and the processor are started by sending the address of the memory location to be accessed to the memory unit and issuing the appropriate control signals. The data are then transferred to or from the memory

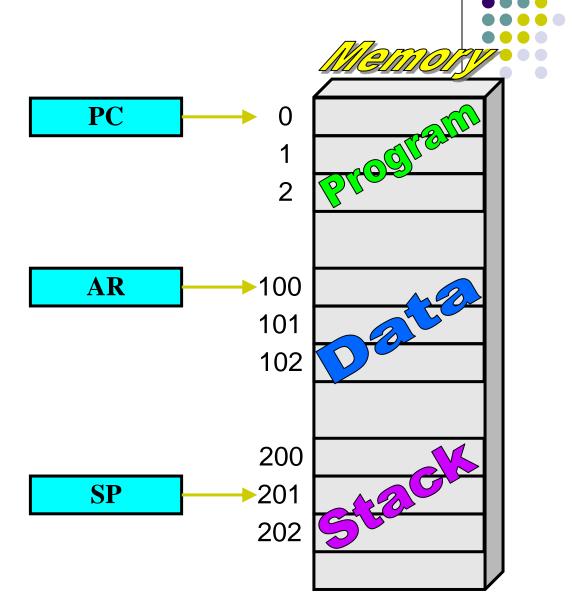

# Connection Between the Processor and the Memory

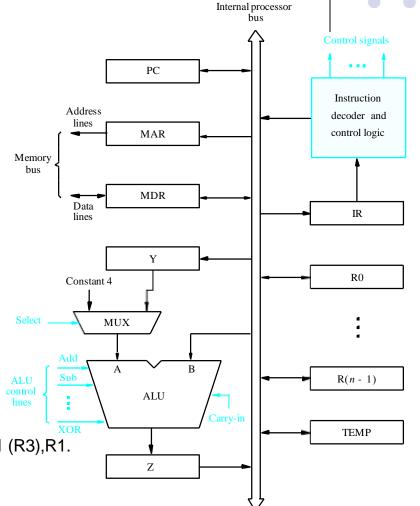

# Registers

- Instruction register (IR)

- Program counter (PC)

- General-purpose register (R<sub>0</sub> R<sub>n-1</sub>)

- Memory address register (MAR)

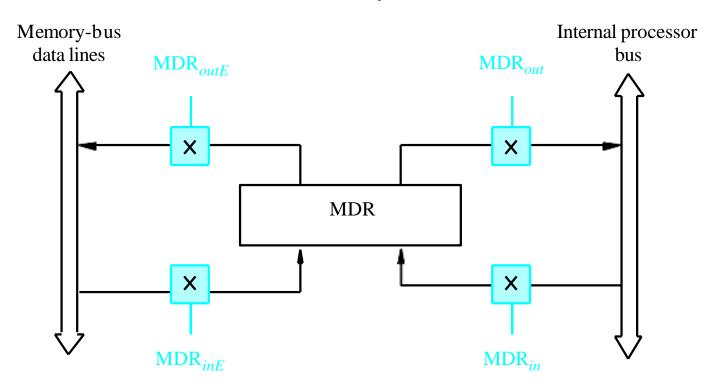

- Memory data register (MDR)

### COMPUTER

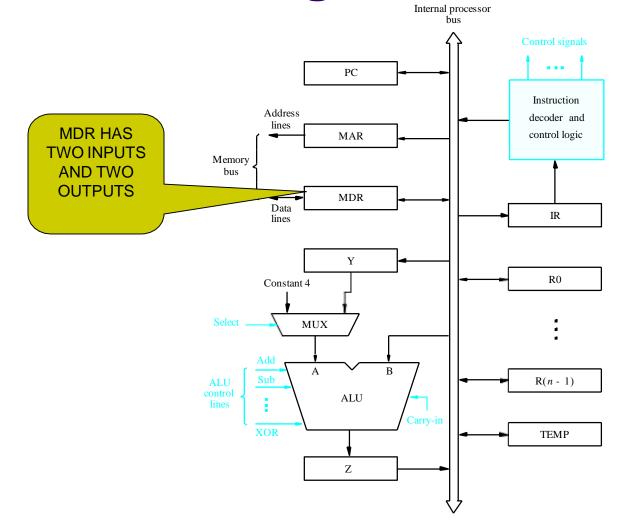

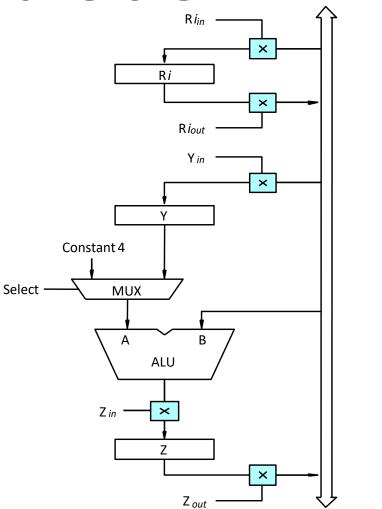

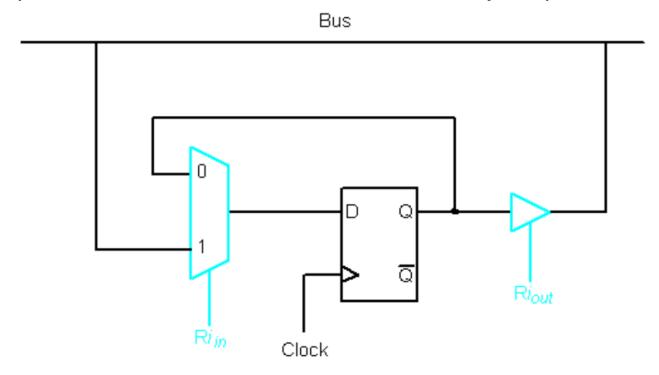

- → The fig shows how memory & the processor can be connected. In addition to the ALU & the control circuitry, the processor contains a number of registers used for several different purposes.

- → The instruction register (IR):- Holds the instructions that is currently being executed. Its output is available for the control circuits which generates the timing signals that control the various processing elements in one execution of instruction.

- → The program counter PC:-

- → This is another specialized register that keeps track of execution of a program. It contains the memory address of the next instruction to be fetched and executed.

- → Besides IR and PC, there are n-general purpose registers R0 through Rn-1.

The other two registers which facilitate communication with memory are: -

- MAR (Memory Address Register):- It holds the address of the location to be accessed.

- 2. MDR (Memory Data Register):- It contains the data to be written into or read out of the address location.

### Operating steps are

- Programs reside in the memory & usually get these through the I/P unit.

- Execution of the program starts when the PC is set to point at the first instruction of the program.

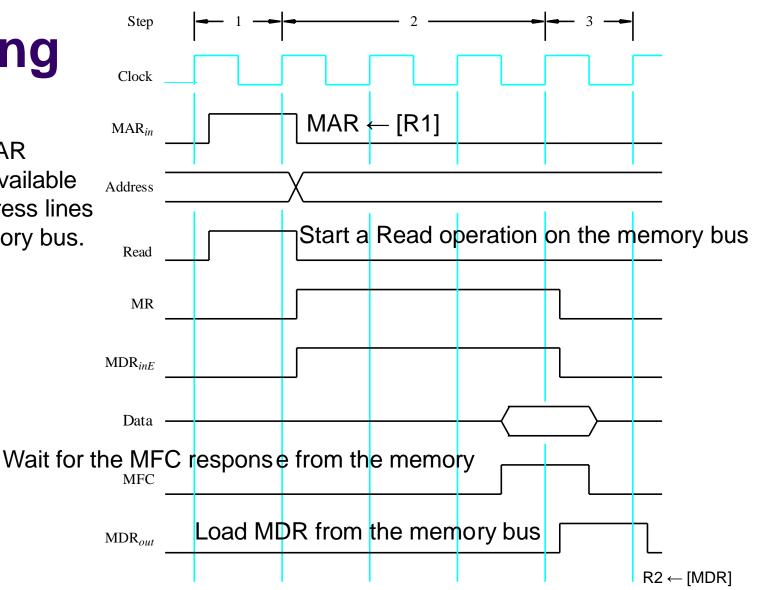

- Contents of PC are transferred to MAR and a Read Control Signal is sent to the memory.

- After the time required to access the memory elapses, the address word is read out of the memory and loaded into the MDR.

- Now contents of MDR are transferred to the IR & now the instruction is ready to be decoded and executed.

- If the instruction involves an operation by the ALU, it is necessary to obtain the required operands.

- An operand in the memory is fetched by sending its address to MAR & Initiating a read cycle.

- When the operand has been read from the memory to the MDR, it is transferred from MDR to the ALU.

- After one or two such repeated cycles, the ALU can perform the desired operation.

- 10. If the result of this operation is to be stored in the memory, the result is sent to MDR.

- Address of location where the result is stored is sent to MAR & a write cycle is initiated.

- 12. The contents of PC are incremented so that PC points to the next instruction that is to be executed.

- →Normal execution of a program may be preempted (temporarily interrupted) if some devices require urgent servicing, to do this one device raises an Interrupt signal.

- → An interrupt is a request signal from an I/O device for service by the processor. The processor provides the requested service by executing an appropriate interrupt service routine.

# **BUS STRUCTURES**

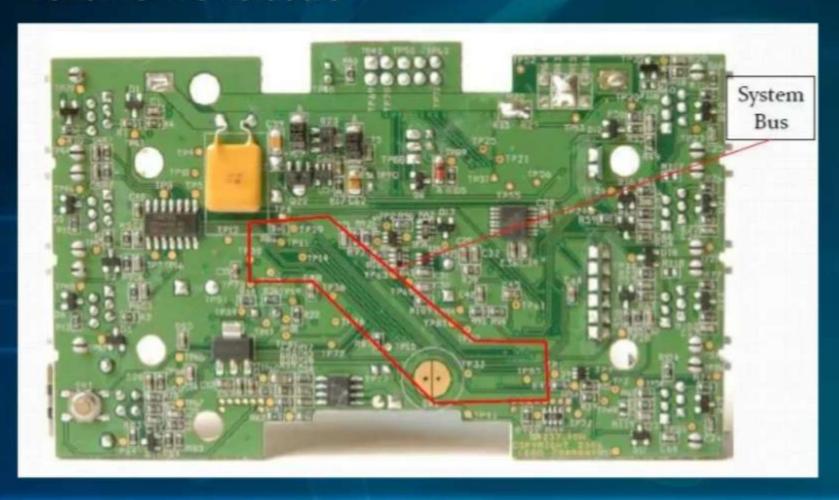

### INTRODUCTION

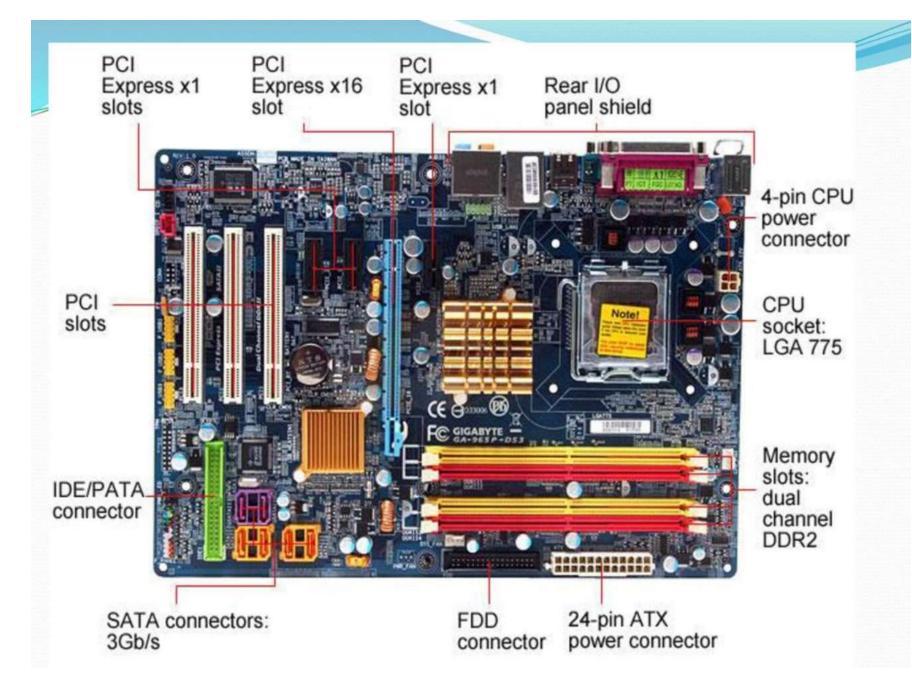

The CPU sends various data values, instructions and information to all the devices and components inside the computer.

If you look at the bottom of a motherboard you'll see a whole network of lines or electronic pathways that join the different components together.

This network of wires or electronic pathways is called the 'Bus'.

# INTRODUCTION (cont'd)

Bottom of motherboard

# BUS

- A bus is a communication pathway connecting two or more devices.

- A key characteristic of a bus is that it is a shared transmission medium.

- Multiple devices connect to the bus, and a signal transmitted by any one device is available for reception by all other devices attached to the bus.

- If two devices transmit during the same time period, their signals will overlap and become garbled. Thus, only one device at a time can successfully transmit.

## BUS cont'd

- Typically, a bus consists of multiple communication pathways, or lines. Each line is capable of transmitting signals representing binary 1 and binary 0.

- several lines of a bus can be used to transmit binary digits simultaneously (in parallel).

- For example, an 8-bit unit of data can be transmitted over eight bus lines.

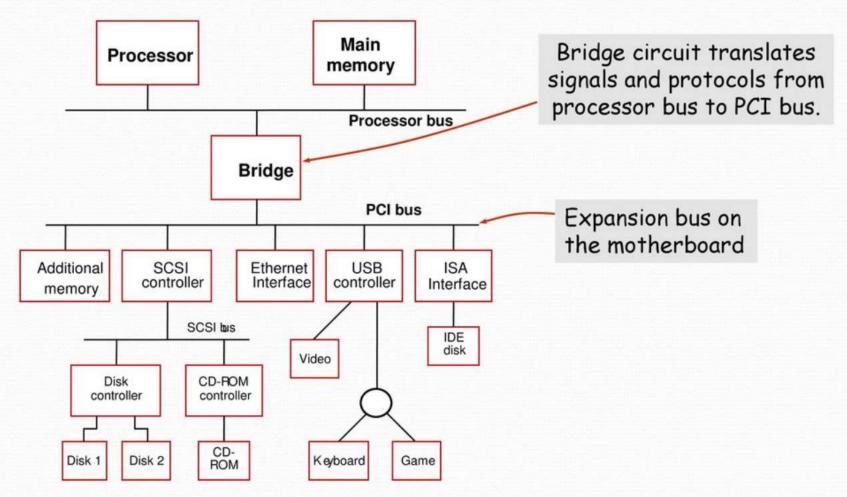

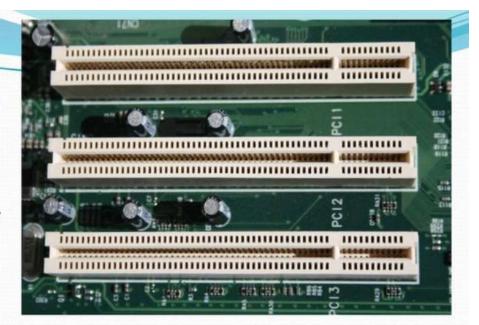

- Computer systems contain a number of different buses that provide pathways between components at various levels of the computer system hierarchy.

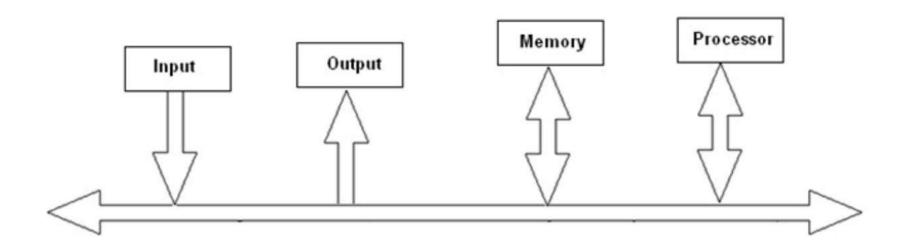

- Bus Structure

- A communication pathway connecting two or more devices

- When a word of data is transferred between units <u>all its bits</u> are <u>transferred in parallel</u>

- ie. The bits are transferred simultaneously over many lines, one bit per line.

- A group of lines that serves as a connecting path for several devices is called a <u>bus</u>

- A group of lines connected to different devices is called bus .

- Bus can carry data and control signals

- Single bus simple way to interconnect functional units .

Single Bus Structure

- All units are connected to this bus

- Bus can used only for one transfer at a time

- So only 2 units can actively use the bus at any given time.

- Only one device at a time can successfully transmit.

- Single bus low cost and It is flexible for attaching diff devices

- By using multiple bus simultaneously can transfer more than one data at a time

- This leads to increase the performance of the system.

- So the bus can carry several data at a time in parallel such as

- Power

- Instructions

- Data

- Addresses

- Commands

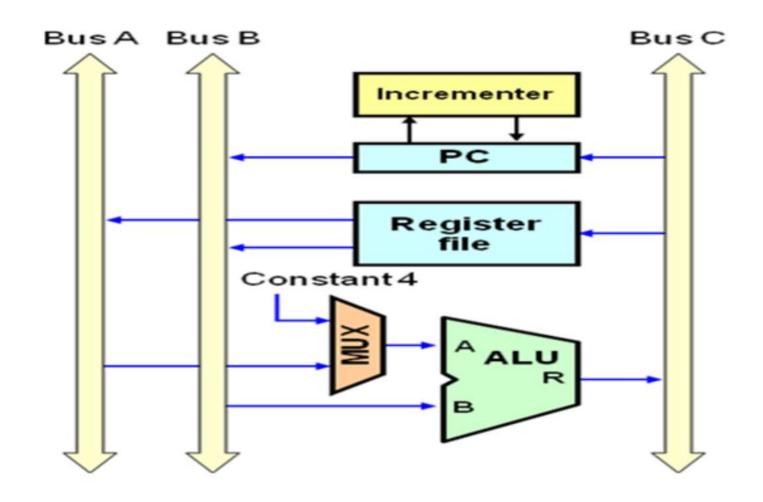

- Multiple-Bus Organization

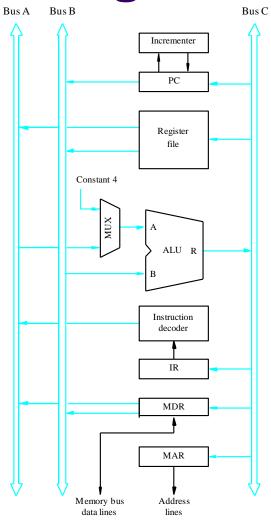

- The following Figure shows a three-bus structure.

- All registers are combined into a single block called register file with three ports: 2 outputs allowing 2 registers to be accessed simultaneously.

- Buses A and B are used to transfer source operands to the A and B inputs of ALU, and result transferred to destination over bus C.

- Diff units in a system having diff speed

- Keyboard

- Printer are relatively slow

- some units are very fast all these devices communicate with each other over the same bus

- in order to communicate all types of units smoothly include buffer registers with the devices to hold the data during transfer.

- eg transfer of data between processor and printer

- Processor sent data over the bus to printer buffer

- Once the buffer is loaded the printer can start printing

With out the interaction of the processor

- The bus and processor are now free to do another work.

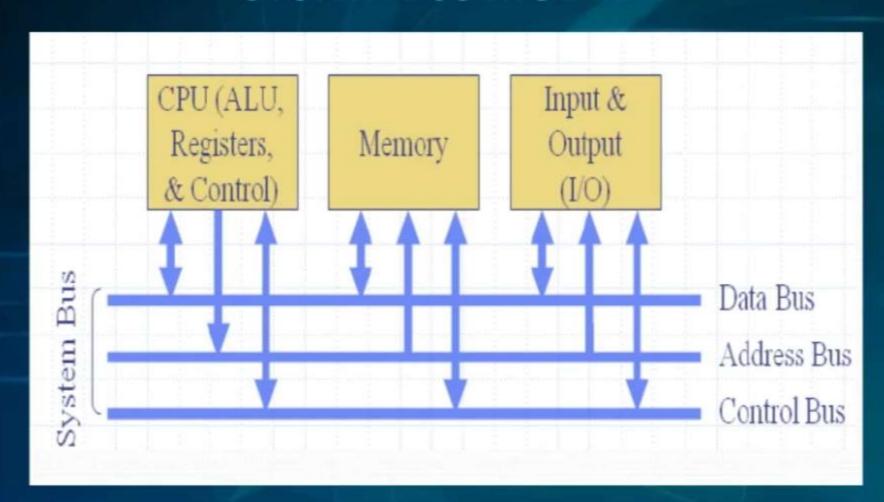

# SYSTEM BUS

- A bus that connects major computer components (processor, memory, I/O) is called a system bus.

- A system bus consists, typically, of from about fifty to hundreds of separate lines. Each line is assigned a particular meaning or function

- System bus usually is separated into three functional groups.

- Data Bus

- Address Bus

- Control Bus.

- In addition, there may be power distribution lines that supply power to the attached modules.

# SYSTEM BUS MODEL

## **DATA BUS**

- A collection of wires through which data is transmitted from one part of a computer to another.

- Data Bus can be thought of as a highway on which data travels within a computer.

- This bus connects all the computer components to the CPU and main memory.

- The data bus may consist of 32, 64, 128, or even more separate lines.

- The number of lines being referred to as the width of the data bus. Because each line can carry only 1 bit at a time, the number of lines determines how many bits can be transferred at a time.

# DATA BUS cont'd

- It is a bidirectional bus.

- The size (width) of bus determines how much data can be transmitted at one time.

- E.g.

- A 16-bit bus can transmit 16 bits (2 bytes) of data at a time.

- 32-bit bus can transmit 32 bits(4 bytes) at a time.

- The size (width) of bus is a critical parameter in determining system performance.

- The wider the data bus, the better, but they are expensive.

## **ADDRESS BUS**

A collection of wires used to identify particular location in main memory is called Address Bus.

Or in other words, the information used to describe the memory locations travels along the address bus.

Clearly, the width of the address bus determines the maximum possible memory capacity of the system.

N address lines directly address 2<sup>N</sup> memory locations.

# ADDRESS BUS cont'd

It is an unidirectional bus.

The CPU sends address to a particular memory locations and I/O ports.

The address bus consists of 16, 20, 24 or more parallel signal lines.

#### **ADDRESS BUS cont'd**

- 8086: 20 address lines

- Could address 1 MB of memory

- Pentium: 32 address lines

- Could address 4 GB of memory

- Itanium: 64 address lines

- Could address 264 bytes of memory

#### CONTROL BUS

- Because the data and address lines are shared by all components, there must be a means of controlling their use.

- The control lines regulates the activity on the bus.

- Control signals transmit both command and timing information among system modules.

- The control bus carries signals that report the status of various devices.

#### CONTROL BUS

- Typical control bus signals are :

- Memory Read: causes data from the addressed location to be placed on the data bus.

- Memory Write: causes data on the bus to be written into the addressed location

- I/O write: causes data on the bus to be output to the addressed I/O port

- I/O read: causes data from the addressed I/O port to be placed on the bus

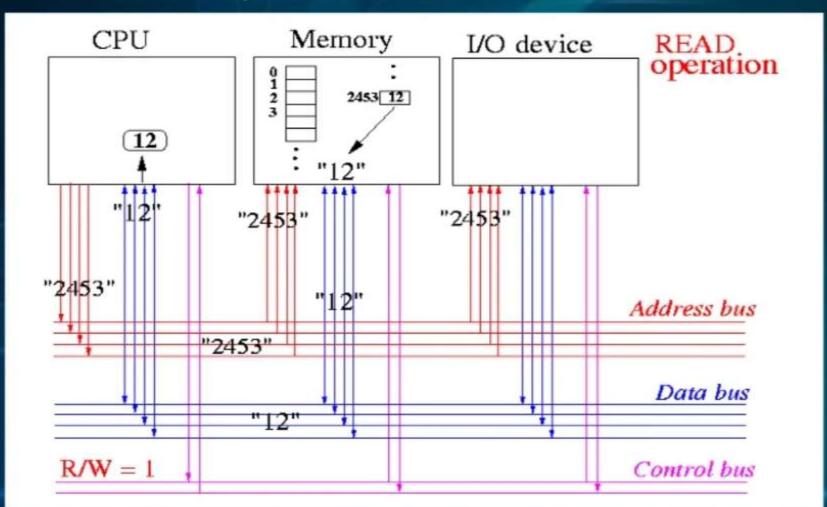

#### Example: Memory Read

The following figure shows how the CPU reads the value 12 from the memory location 2453:

#### Example: Memory Read cont'd

- CPU sends out the address value 2453 on the address bus

- Simultaneously, CPU sends out the signal R/W = 1 on the control bus, which indicates a READ operation

- CPU then waits for the data from memory on the data bus

- The R/W = 1 signal and the address bus value 2453 will cause the memory to retrieve the value at memory location 2453 to be sent out on the data bus

### Memory Read a Closer look

- Address of next instruction is in PC

- Address (MAR) is placed on address bus

- Control unit issues READ command

- Result (data from memory) appears on data bus

- Data from data bus copied into MBR

- PC incremented by 1.

- Data (instruction) moved from MBR to IR

- MBR is now free for further data fetches

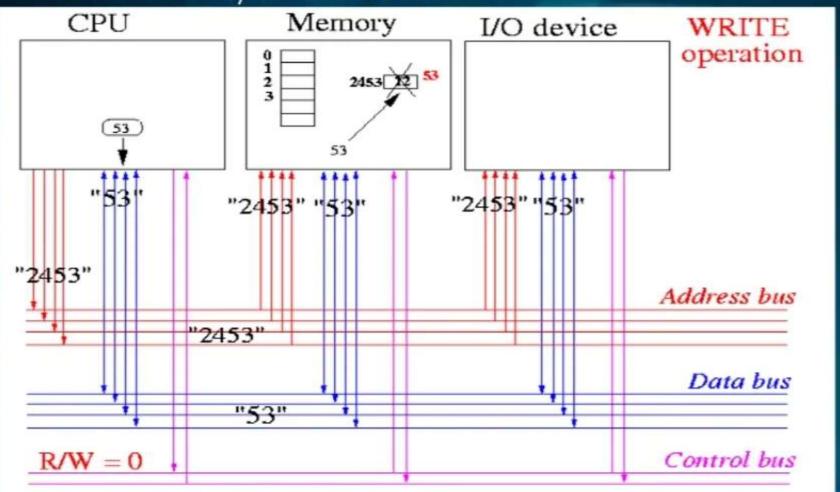

#### **Example: Memory Write**

The following figure shows how the CPU writes the value 53 from the memory location 2453:

### Example: Memory Write cont'd

- CPU sends out the address value 2453 on the address bus

- Simultaneously, CPU also sends out the value 53 on the data bus

- And the signal R/W = 0 on the control bus which indicating a WRITE operation

- The R/W = 0 signal along with the address bus value 2453 and data bus value 53 will cause the memory to store the value 53 at the location 2453...

#### Control Bus cont'd

- Control lines also include :

- Transfer ACK: indicates that data have been accepted from or placed on the bus.

- Bus request: indicates that a module needs to gain control of the bus.

- Bus grant: indicates that a requesting module has been granted control of the bus.

#### Control Bus cont'd

- Interrupt request: indicates that an interrupt is pending.

- Interrupt ACK: acknowledges that the pending interrupt has been recognized.

- Reset: initializes all modules.

#### Bus Design Issues

- Need to consider several design issues :

- \* Bus width

- » Data and address buses.

- \* Bus type

- » Dedicated or multiplexed.

- \* Bus operations

- » Read, write, block transfer, interrupt, ...

- \* Bus arbitration

- » Centralized or distributed.

- \* Bus timing

- » Synchronous or asynchronous

### **Bus Type**

- Dedicated buses

- Separate buses dedicated to carry data and address information.

- Good for performance.

- But increases cost.

- Multiplexed buses

- Data and address information is time multiplexed (defined in the next slide) on a shared bus.

- Poor Performance

- But Reduces cost.

#### **Bus Operations**

- Basic operations

- Read and write.

- Block transfer operations.

- Read or write several contiguous memory locations.

- Example: cache line fill.

- Interrupt operation.

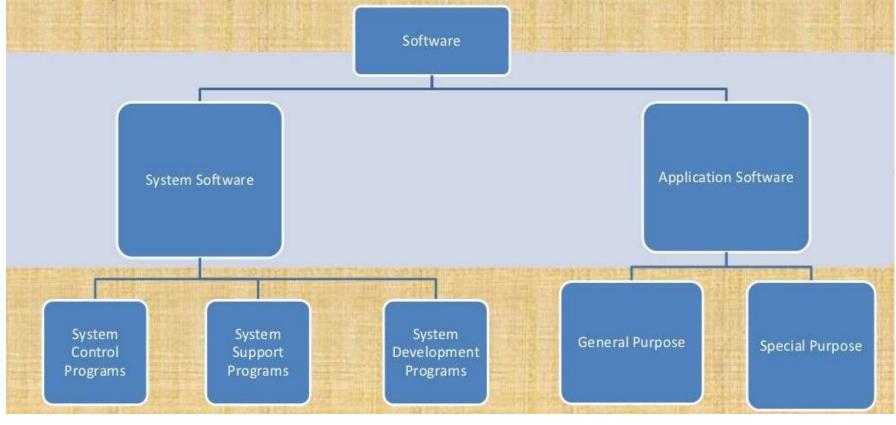

#### **SOFTWARE**

Software is a set of computer programs which are designed and developed to perform specific task desired by the user or by the computer itself.

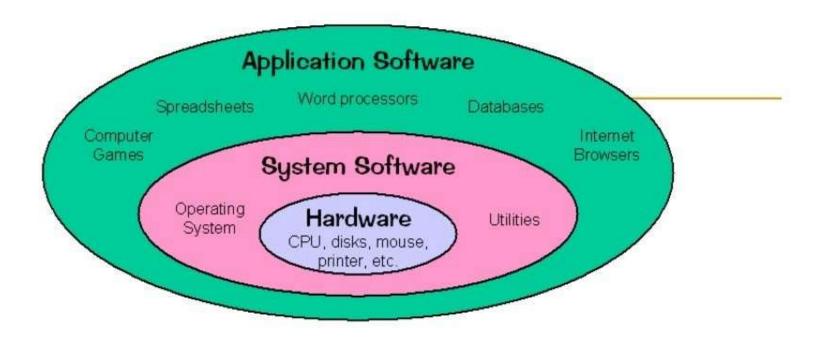

### Types of Software

- System Software

- Application Software

#### Software?

#### Software

Computer Instructions or data, anything that can be stored electronically is **Software**.

#### Examples:-

Ms word, excel, power point, spread sheets, library management system etc.

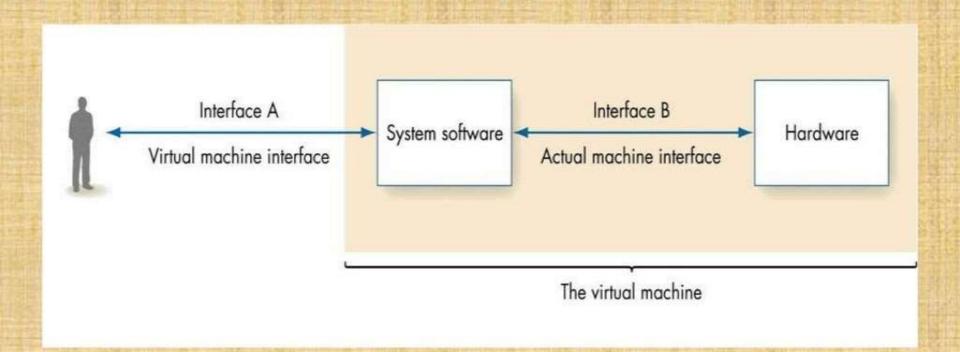

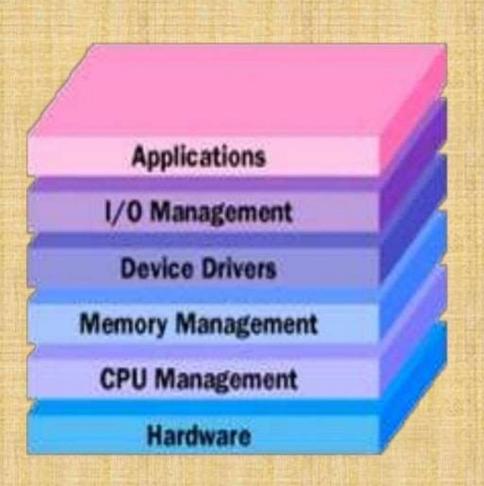

# System Software

- The system software is collection of programs designed to operate, control and extend the processing capabilities of the computer itself.

- These are generally prepared by computer manufacturers.

- These software perform a variety of functions like file editing, storage management, resource accounting, I/O management, etc.

### **Role of System Software**

# **Types of System Software**

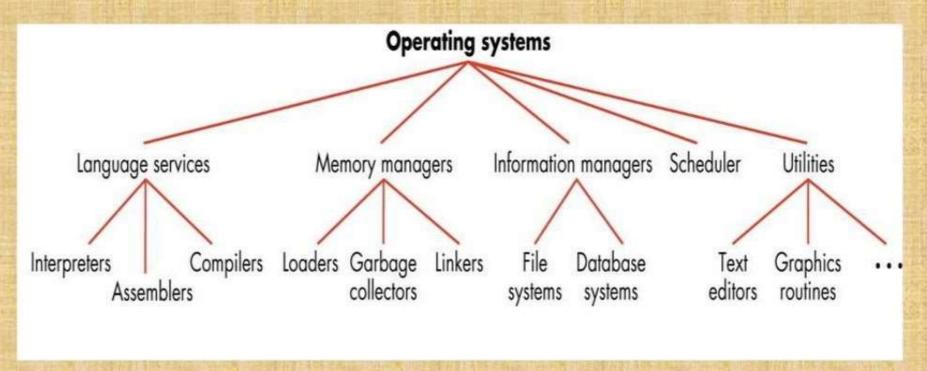

#### System Control Programs :

They control the execution of programs, manage the storage and processing resources of the computer and perform other management and monitoring functions. e.g., OS

#### 2. System Support Programs:

They provide routine service functions to other computer programs and computer users. e.g., Utility Programs

#### 3. System Development Programs:

They assist in the creation of publication programs.

e.g., Language translators like interpreters, compilers and assemblers

# **System Control Programs-OS**

An operating system is an integrated set of specialized programs that are used to manage overall resources of and operations of the computer.

### Operating System contd...

#### Main functions-

- Memory Management

- Processor Management

- Device Management

- File Management

- Security

- Control over system performance

- Job Accounting

#### **Operating System**

- An operating system is software which manages computer hardware and software resources. It also provides common services to computer programs.

- The operating system is an essential component of the system software in a computer system. Application programs are dependent on operating system to function

# <u>Utilities</u>

Utilities software is system software which is manufactured to help ,analyze, configure, optimize or to maintain a computer.

It also helps in maintenance and problem solving of a computer.

# Common types of utility programs

- Hardware utilities

- Virus-detection and recovery utilities

- File-compression utilities

- Spam and pop-up blocker utilities

- Backup

- Uninstall

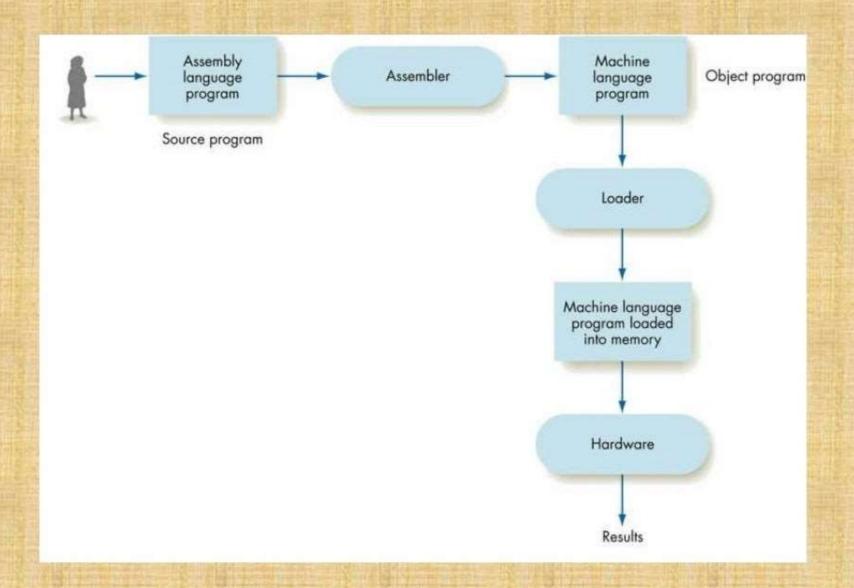

# System Development Programs-Language Translators

Language translators are also called language processors.

#### Main functions are:

- Translate high level language to low level language.

- Check for and identity syntax errors that may be present in the program being installed.

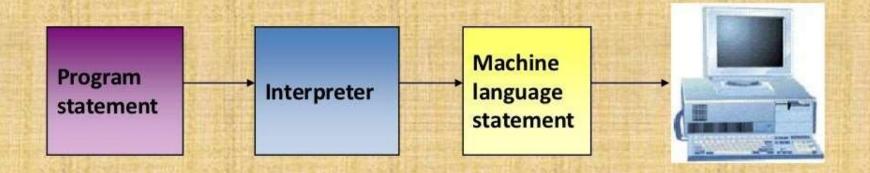

#### There are 3 types of translator programs-

- 1. Assembler

- 2. Interpreter

- 3. Compiler

#### Assembler

Translates a source program into a corresponding object program.

#### Assembler tasks

- Convert symbolic op codes to binary

- Convert symbolic addresses to binary

- Perform assembler services requested by the pseudo-ops

- Put translated instructions into a file for future use

#### How an Assembler works...

### Interpreter

• A language translator that translates one program statement at a time into machine code.

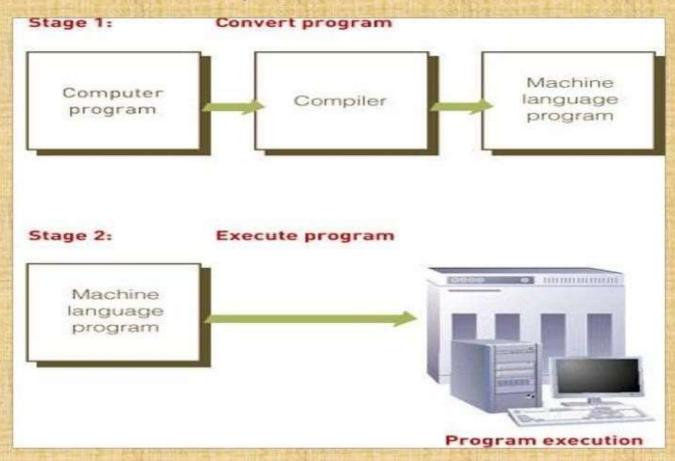

### Compiler

A language translator that converts a complete program into machine language to produce a program that the computer can process in its entirely

#### **Device Drivers**

- Device driver is actually a communication device between device and computer

- It loads every time in memory

- When a new device is added the driver should be installed in order to run the program

### Features of System Software

- Close to system

- Fast in speed

- Difficult to design

- Difficult to understand

- Less interactive

- Smaller in size

- Difficult to manipulate

- Generally written in low level language

### **Application Software:**

Application Software includes programs that do real work for user.

#### Example:

Payroll systems, Inventory Control, Manage student database, Word Processor, Spreadsheet and Database Management System etc.,

# **Application Software**

- Actually the application software consists of programs that are designed to make users more comfortable or productive to assist personal tasks

- The application software is present on computer hard disk

- Application software can also be stored on CDs, DVDs, and flash or keychain storage devices

# **Application Software**

Categories of Application Software

Types of Application

Forms of Application Software

# <u>Categories of Application</u> <u>Software</u>

Business Software

Graphic & Multimedia

Home / Personal / Education

Communication

# Types of Application Software

- Proprietary

- In-house

Contract

Off-the-shelf

Customized package

## Forms of Application

## S Packaged Software

- Custom Software

- Web Application

- Open Source

- Shareware

- Freeware

- Public-domain Software

## Form Of Application Software

Package software

A software which is sold in a bundle due to similar function of programs.

- Example

- Microsoft office, windows Cd

#### **Custom Software**

This is software which is specially made for an organization as per their requirement.

#### Example

- Attendance system

- Security code system.

## Web Application

A web application is any application that uses a web browser.

#### **Example**

Google docs

Drop Box

## Open source software

Open source software is made available to every one and can be change, modify and distribute to public without any notification.

#### Example

- Linux

- Moodle

- III. Wordpress

- Ⅳ. Drupal

moodle

### Free ware

Free ware is the software that is freely available to public but author has a copy right, means that you can only use it ,not sell

it.

Example

Antivirus

## Public domain software

Public domain software is totally free and it is not copyrighted plus it have no restriction

#### **Example**

- SQlite

- II. Blast

- III. I2P

# Computer Performance

#### **Performance**

- The most important measure of a computer is how quickly it can execute programs.

- Three factors affect performance:

- Hardware design

- Instruction set

- Compiler

#### **Performance**

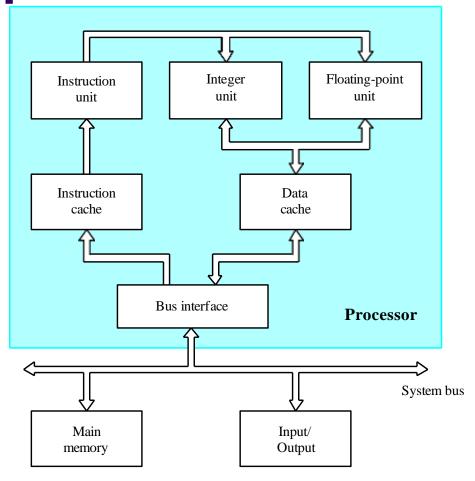

Processor time to execute a program depends on the hardware involved in the execution of individual machine instructions.

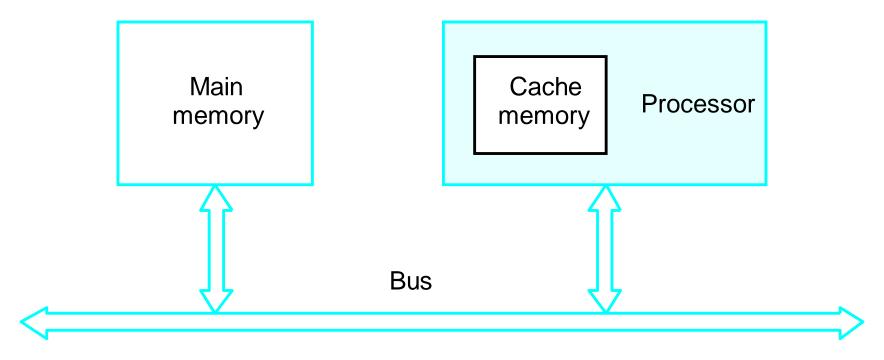

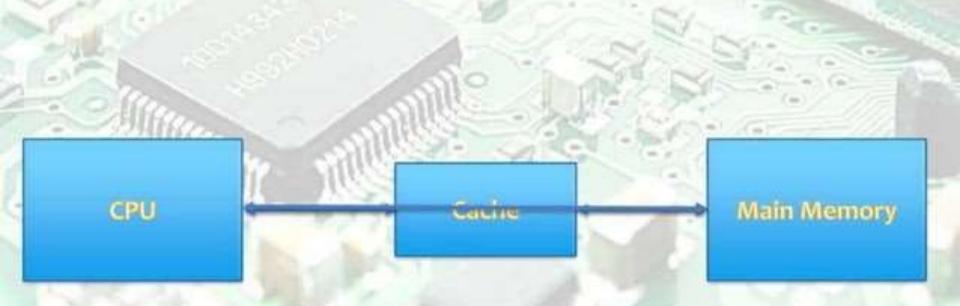

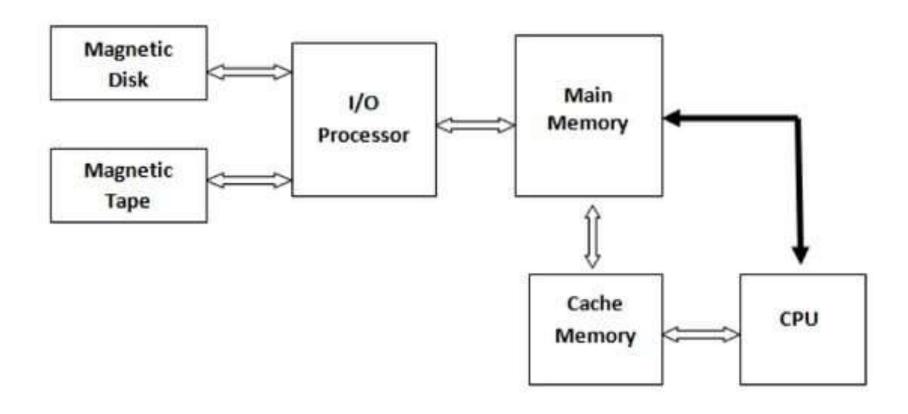

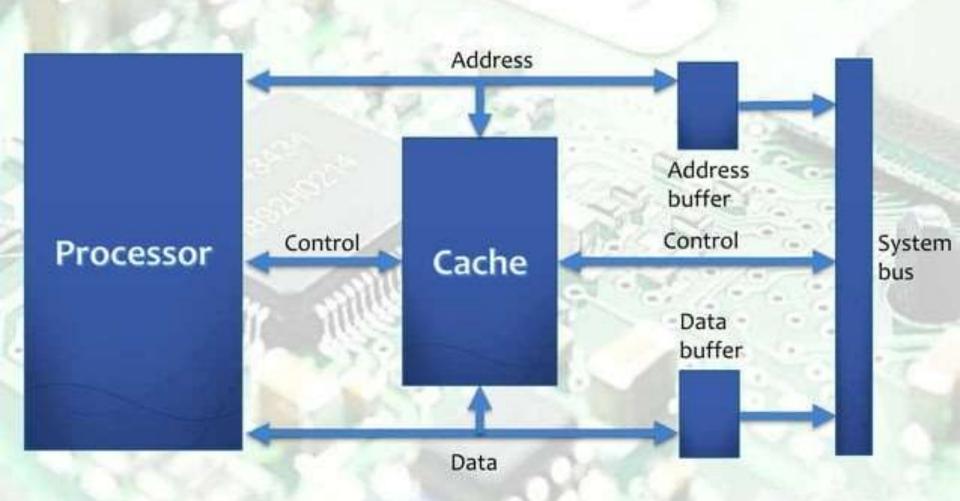

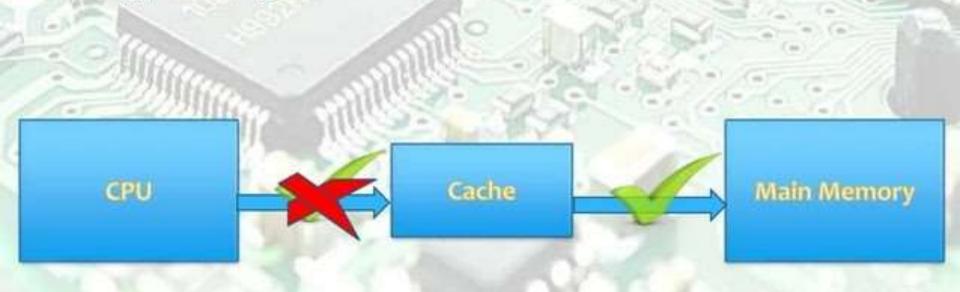

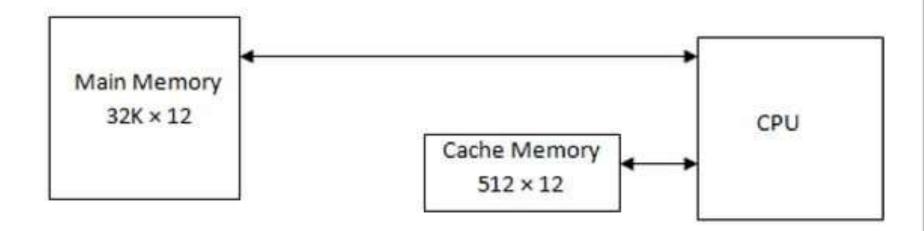

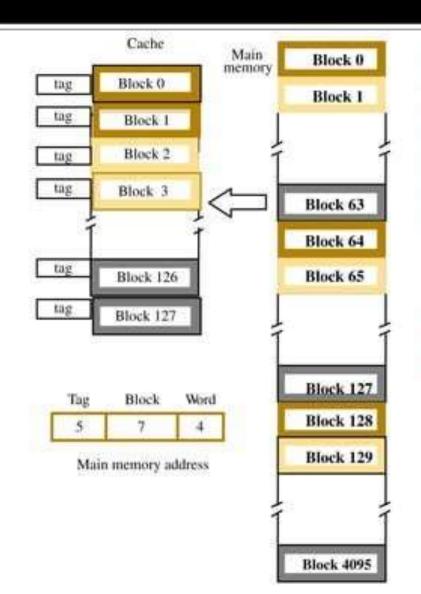

Figure 1.5. The processor cache.

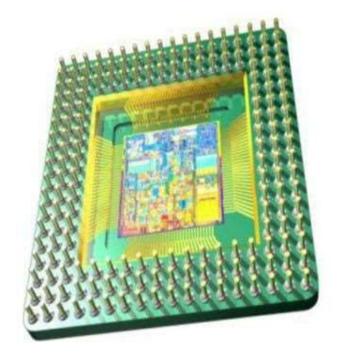

#### **Performance**

- The processor and a relatively small cache memory can be fabricated on a single integrated circuit chip.

- Speed

- Cost

- Memory management

#### **Processor Clock**

- Clock, clock cycle, and clock rate

- The execution of each instruction is divided into several steps, each of which completes in one clock cycle.

- Hertz cycles per second

- T processor time required to execute a program that has been prepared in high-level language

- N number of actual machine language instructions needed to complete the execution (note: loop)

- S average number of basic steps needed to execute one machine instruction. Each step completes in one clock cycle

- R clock rate

- Note: these are not independent to each other

$$T = \frac{N \times S}{R}$$

How to improve T?

## Pipeline and Superscalar Operation

- Instructions are not necessarily executed one after another.

- The value of S doesn't have to be the number of clock cycles to execute one instruction.

- Pipelining overlapping the execution of successive instructions.

- Add R1, R2, R3

- Superscalar operation multiple instruction pipelines are implemented in the processor.

- Goal reduce S (could become <1!)</li>

#### **Clock Rate**

- Increase clock rate

- Improve the integrated-circuit (IC) technology to make the circuits faster

- Reduce the amount of processing done in one basic step (however, this may increase the number of basic steps needed)

- Increases in R that are entirely caused by improvements in IC technology affect all aspects of the processor's operation equally except the time to access the main memory.

#### **CISC** and RISC

- Tradeoff between N and S

- A key consideration is the use of pipelining

- S is close to 1 even though the number of basic steps per instruction may be considerably larger

- It is much easier to implement efficient pipelining in processor with simple instruction sets

- Reduced Instruction Set Computers (RISC)

- Complex Instruction Set Computers (CISC)

## Compiler

- A compiler translates a high-level language program into a sequence of machine instructions.

- To reduce N, we need a suitable machine instruction set and a compiler that makes good use of it.

- Goal reduce N×S

- A compiler may not be designed for a specific processor; however, a high-quality compiler is usually designed for, and with, a specific processor.

#### **Performance Measurement**

- T is difficult to compute.

- Measure computer performance using benchmark programs.

- System Performance Evaluation Corporation (SPEC) selects and publishes representative application programs for different application domains, together with test results for many commercially available computers.

- Compile and run (no simulation)

- Reference computer

$$SPEC\ rating = rac{Running}{Running}$$

time on the reference computer under test

$$SPEC\ rating = \left(\prod_{i=1}^{n} SPEC_{i}\right)^{\frac{1}{n}}$$

## Why Study Performance?

- Make intelligent design choices

- See through the marketing hype

- Key to understanding underlying computer organization

- Why is some hardware faster than others for different programs?

- What factors of system performance are hardware related? (e.g., Do we need a new machine, or a new operating system?)

## Computer performance

Computer performance is characterized by the amount of useful work accomplished by a computer system compared to the time and resources used.

## Computer performance

Depending on the context, good computer performance may involve one or more of the following:

- Short response time for a given piece of work

- High throughput (rate of processing work)

- Low utilization of computing resource(s)

- High availability of the computing system or application

- Fast (or highly compact) data compression and decompression

- High bandwidth / short data transmission time

## Computer vs H/W Performance

- Latency/Response Time (clocks from input to corresponding output)

- —How long does it take for my program to run?

- —How long must I wait after typing return for the result?

- Throughput (How many results per clock)

- —How many results can be processed per second?

- —What is the average execution rate of my program?

- —How much work is getting done?

If we upgrade a machine with a new processor what do we improve?

Response Time/Latency

If we add a new machine to the lab what do we increase?

Throughput

## **Design Tradeoffs**

- Maximum Performance: measured by the numbers of instructions executed per

Second

- Minimum Cost: measured by the size of the circuit.

- Best Performance/Price: measured by the ratio of MIPS to size. In powersensitive applications MIPS/Watt is important too.

## Aspect of software quality

Computer software performance, particularly software application response time, is an aspect of software quality that is important in human–computer interactions.

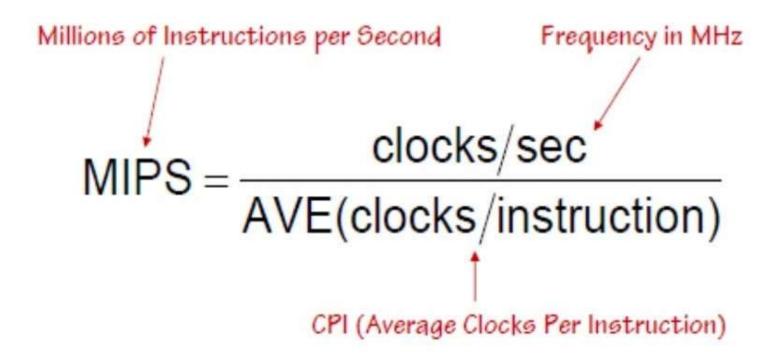

#### **Performance Equation**

The total amount of time (t) required to execute a particular benchmark program is

$$t = N * C/f$$

, or equivalently

P = I \* f/N

#### where

- P = 1/t is "the performance" in terms of time-toexecute

- N is the number of instructions actually executed (the instruction path length).

- f is the clock frequency in cycles per second.

- C= is the average cycles per instruction (CPI) for this benchmark.

- I= is the average instructions per cycle (IPC) for this benchmark.

## **Performance Equation**

An another performance equation- The equation, which is fundamental to measuring computer performance is:

where the time per program is the required CPU time.

#### Comparing the performance of two systems

In comparing the performance of two systems we measure the time that it takes for each system to perform the same amount of work. If the same program is run on two systems, System A and System B, System A is *n times as fast* as System B if:

running time on system B =

$$n$$

.

running time on system A

#### Comparing the performance of two systems

System A is x% faster than System B if:

$$\left(\frac{\text{running time on system B}}{\text{running time on system A}} - 1\right) \times 100 = x.$$

These formulas are useful in comparing the average performance of one system with the average performance of another.

#### **Execution Time**

Elapsed Time/Wall Clock Time

counts everything (disk and memory accesses, I/O, etc.)

a useful number, but often not good for comparison purposes

CPU time

Doesn't include I/O or time spent running other programs can be broken up into system time, and user time

Our focus: user CPU time

Time spent executing actual instructions of "our" program

## **Computer Performance Measure**

## **How to Improve Performance?**

So, to improve performance (everything else being equal) you can either

Decrease the # of required cycles for a program, or (improve ISA/Compiler)

Decrease the clock cycle time or, said another way,

Increase the clock rate. (reduce propagation delays or use pipelining)

Decrease the CPI (average clocks per instruction) (new H/W)

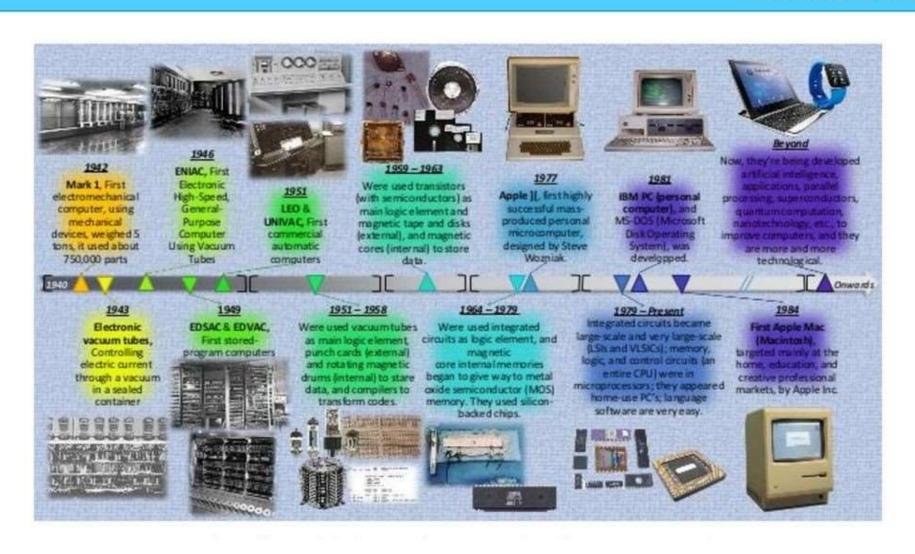

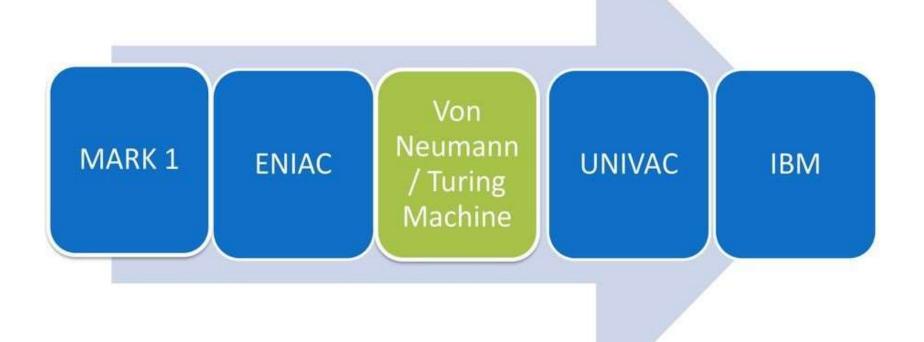

#### THE HISTORY OF COMPUTER DEVELOPMENT

- A long time ago, human are using their fingers, stones etc to do calculation.

- At the same time, they are trying to create an apparatus that could facilitate the calculation process.

- After a few trial, finally the complex and advance calculation system has been produced and it is known as a computer.

The History & Evolution Of Computer Basically, the history of computer development is divided into 2 parts:

before 1940 & after 1940.

## **BEFORE 1940**

## **Abacus Counting Device**

- Created on 3000 B.D. at Babylonia.

- Was the first mechanical counting device in the world.

- Able to execute addition and subtraction operation.

## John Napier's Bone

- Created on 1614 by John Napier.

- Facilitate multiplication and division processes – faster & easier.

- The first logarithm table has been created.

#### Pascaline Machine

- Created on 1642 by Braise Pascal.

- Was the first mechanical machine or calculator in the world.

- Able to execute addition and subtraction

processes.

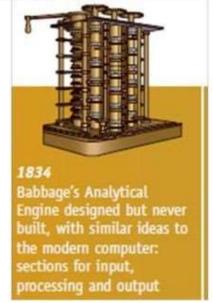

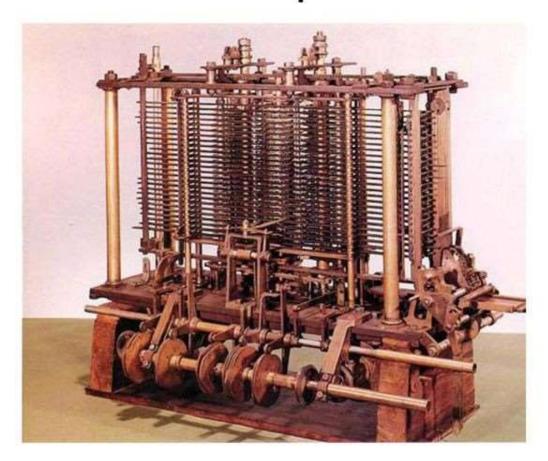

## **Babbage Differentiation Machine**

- Created by Charles Babbage on 1821.

- Was the first mechanical machine which is used the steam power.

- Able to do a calculation and printing the output automatically.

Babbage Analytical Engine

- It has five (5) main parts:

- Input unit

- Output unit

- Processing Unit

- Control unit

- Memory unit

- His invention has became a theory model for today's computer technology. Because of that, Charles Babbage has been known as The Ancestor of A Modern Computer

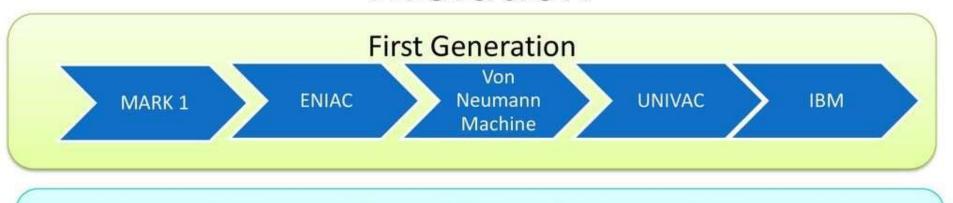

## **After 1940**

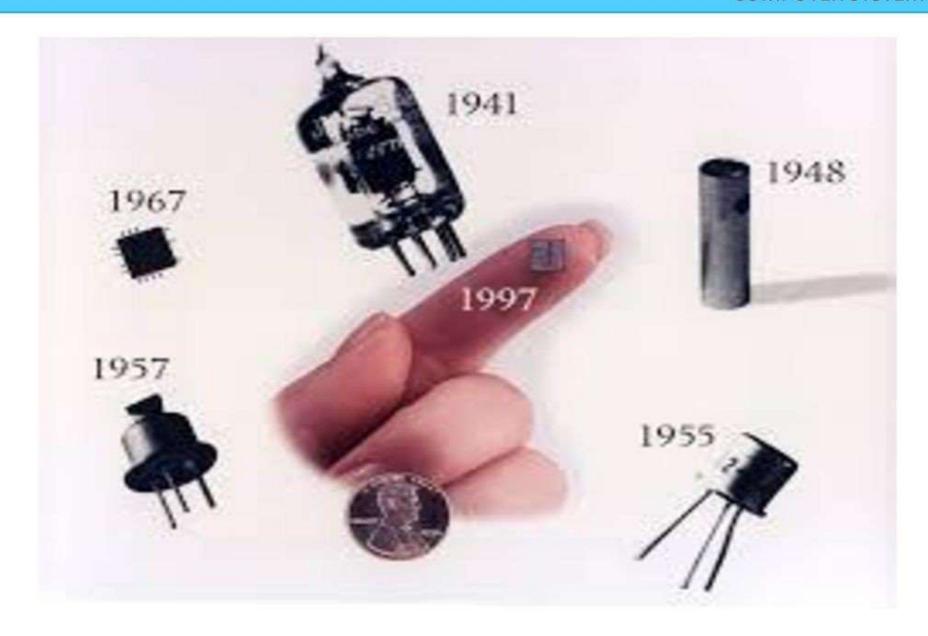

#### **Evolution**

Second Generation

**Transistors**

**Third Generation**

Integrated Circuit

**Later Generation**

Microprocessor

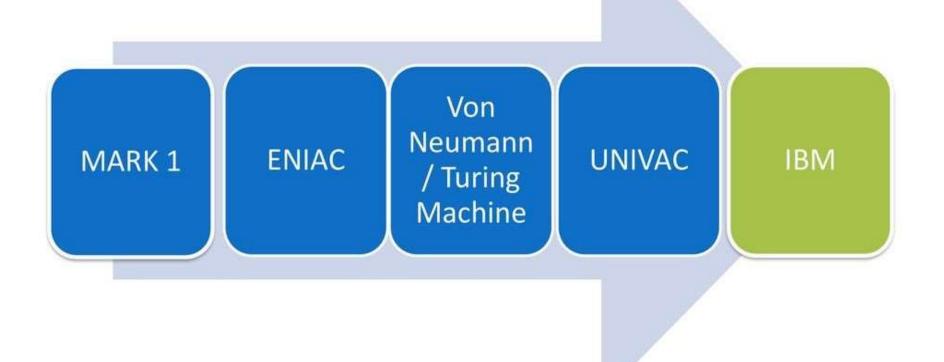

#### COMPUTER SYSTEM

#### Mark 1

- Created on 1941 by Dr. Howard Aikern in conjunction with IBM.

- Was the first electro-mechanical computer.

- Size: 55 feet long, 8 feet height and connected with 800 km of wire.

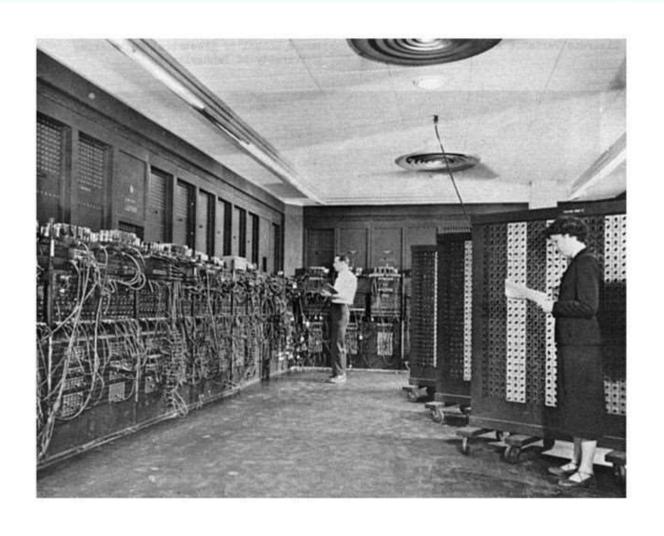

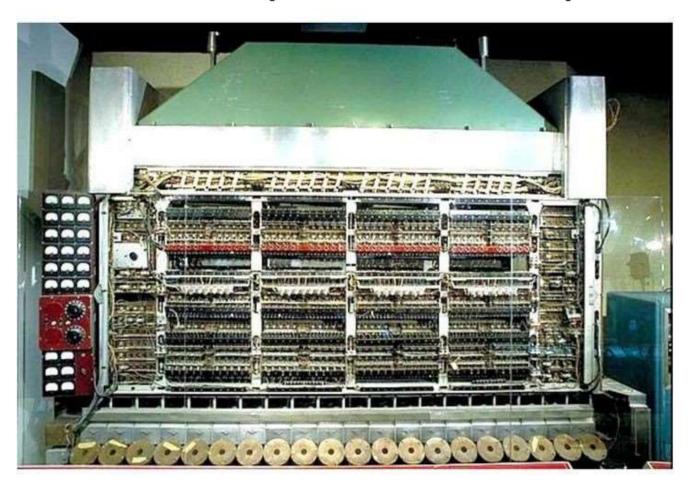

#### **ENIAC**

- Electronic Numerical Integrator And Computer

- Eckert and Mauchly

- University of Pennsylvania

- Trajectory tables for weapons

- Started 1943

- Finished 1946

- ENIAC was created to help with the war effort against German forces. Used until 1955

#### **ENIAC**

- Decimal (not binary)

- 20 accumulators of 10 digits

- Programmed manually by switches

- 18,000 vacuum tubes

- 30 tons

- 15,000 square feet

- 140 kW power consumption

- 5,000 additions per second

- 1000 times faster than Mark 1.

#### COMPUTER SYSTEM

## Stored-program concept

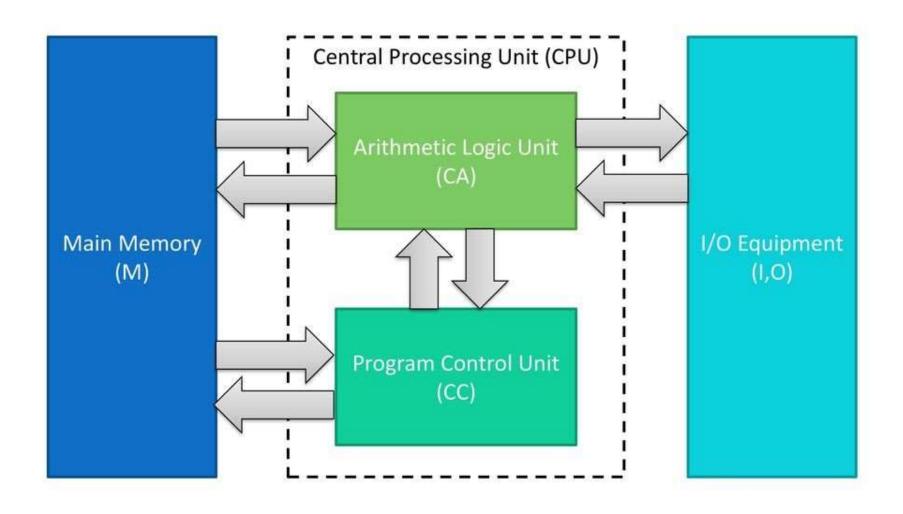

The task of entering and altering program is tedious for ENIAC. Suppose a program could be represented in a form suitable for storing in memory alongside data. Then computer could get its instruction by reading them from memory and program could be set or altered by settings the values of a portion of memory. This idea is known as stored-program concept an developed by Von Neumann referred to IAS computer.

## Von Neumann / Turing Machine

- Stored Program concept

- Main memory storing programs and data

- ALU operating on binary data

- Control unit interpreting instructions from memory and executing

- Input and output equipment operated by control unit

## Von Neumann / Turing Machine - Example

#### Von Neumann Machine - Structure

### Von Neumann earlier proposal

- First since the device is primarily a computer, it will have to perform addition, subtraction, multiplication or addition therefore it need special organs to do it, therefore come the CA

- Second- The logical control of the device that is the proper sequencing of its operation, carried out by central control organ, therefore come the second part, CC

## Von Neumann earlier proposal

- Third Any device that is to carried out long and complicated operation need considerable memory, therefore come the third specific part of the device, M

- These three specific part called CC, CA and M correspond to the associative neurons nervous system

- Fourth- The device need an organ to transfer from R to specific part of C or M, these organ form its input called, I.

- Fifth The device must have an organ to transfer from C or M to R outside specific medium. These organ form O, output.

## Von Neumann / Turing Machine (2)

- Princeton Institute for Advanced Studies

- IAS

- Completed 1952

#### IAS

- 1000 x 40 bit words

- Binary number

- 2 x 20 bit instructions

- Set of registers (storage in CPU)

- Memory Buffer Register contains word to be stored/received from in memory or sent to i/o unit.

- Memory Address Register specifies the address in memory of the word to be written from or read into MBR.

- Instruction Register contains 8-bit operation code instruction being executed.

- Instruction Buffer Register to hold temporarily the instruction

- Program Counter contain address of the next instruction.

- Accumulator

hold temporarily operands and result of ALU operation.

Multiplier Quotient

#### IAS – Structure

### IAS operation

- The opcode of the next instruction is loaded into the IR and the address portion is loaded into MAR. The instruction may by be taken from IBR or it can be taken from memory by loading a word into MBR, then down to IBR, IR and MAR.

- Once in the IR, the control circuitry interprets the opcode and execute the instruction by sending the right signal to moved the data or an operation to be performed by the ALU.

## IAS Computer - Example

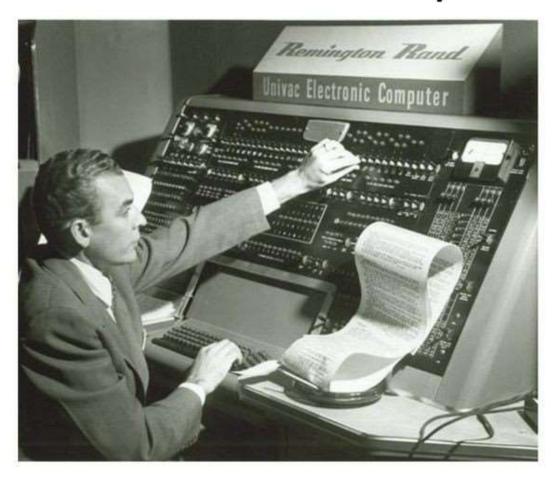

# Universal Automatic Computer (UNIVAC)

1947 UNIVAC I Eckert-Mauchly Formed Computer Corporation

(to manufacture computer commercially)

Late 1950 UNIVAC II Part of Sperry-Rand Corporation

Faster & more memory

#### UNIVAC

- UNIVAC I the first successful commercial computer. Used for scientific and commercial application ie, matrix algebraic computation, statistical problem, premium billings, or life insurance company and logistic problem.

- UNIVAC II greater memory capacity and higher performance

## **UNIVAC - Example**

### **Second Generation Machine**

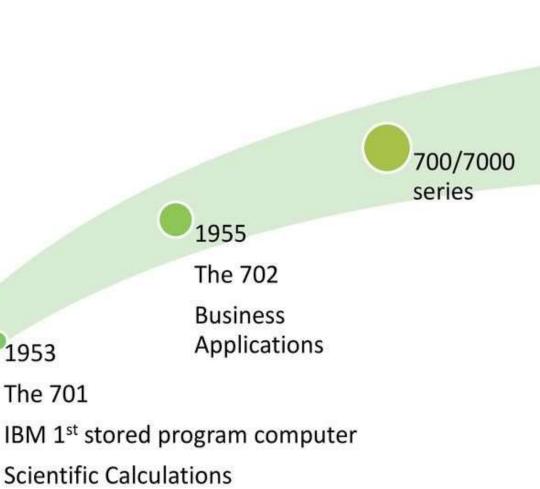

#### **IBM**

1953

The 701

### **IBM 701**

## **IBM 702**

## IBM 700/7000

#### **Transistors**

- Made from Silicon (Sand)

- Invented 1947 at Bell Labs

- William Shockley et al.

- Replaced vacuum tubes: wires, metal plates, glass capsule and vacuum.

- Solid State device made from silicon.

#### **Advantages of Transistors**

- Smaller

- Cheaper

- Less heat dissipation

#### **Transistors Based Computers**

- Second generation machines

- NCR & RCA produced small transistor machines

- IBM 7000

- Digital Equipment Corporation(DEC) 1957

- Produced PDP-1 first mini computer phenomenon.

#### **COMPUTER SYSTEM**

#### **Third Generation Machine**

#### Integrated Circuit/Microelectronics

- Literally "small electronics"

- Transistors were replaced by integrated circuits(IC)

- One IC could replace hundreds of transistors

- This made computers even smaller and faster.

#### Integrated circuit

- In 1958, came an achievement that revolutionized electronics and started the era of microelectronic, the invention of integrated circuit, defined the third generation of computer.

- Initially only a few gates and memory cells, could be reliably manufactured together. As time went on, it become possible to pack more and more component on the same chip

- The cost of chip remained unchanged during the period growth of density. This means the cost of memory circuitry has fallen at a dramatic rate

- Because logic and memory elements are placed closer together on more densely packed chips, the electrical path length is shortened, increasing operating speed.

- The computer become smaller

- Reduction in power and cooling requirement

- The interconnection of integrated circuit are more reliable than solder connection.

#### **Later Generation Computers**

#### **Later Generation Computers**

- In 1970 the Intel Corporation invented the Microprocessor: an entire CPU on one chip

- This led to microcomputers-computers on a desk

#### **Later Generation Computers**

- This transformation was a result of the invention of the microprocessor.

- A microprocessor (uP) is a computer that is fabricated on an integrated circuit (IC).

- Computers had been around for 20 years before the first microprocessor was developed at *Intel* in 1971.

#### Microprocessor

- More than 1000 component can be placed on a single integrated chip. VLSI achieved more than 10000 component on single chip.

- Just as density of element of memory chips has continue to rise, so has the density of elements on processor chips. As time went on, more and more elements were placed on each chip, so that fewer and fewer chips were needed to construct. a single computer processor. A breakthrough is achieved on 1971.

#### Intel

| Year | Computer<br>Name | Description                                                                                          |

|------|------------------|------------------------------------------------------------------------------------------------------|

| 1971 | 4004             | <ul> <li>First microprocessor</li> <li>All CPU components on a single chip</li> <li>4 bit</li> </ul> |

| 1972 | 8008             | <ul> <li>8 bit</li> <li>Both designed for specific applications</li> </ul>                           |

| 1974 | 8080             | Intel's first general purpose microprocessor                                                         |

# Chapter 2. Machine Instructions and Programs

#### **Objectives**

- Machine instructions and program execution, including branching and subroutine call and return operations.

- Number representation and addition/subtraction in the 2's-complement system.

- Addressing methods for accessing register and memory operands.

- Assembly language for representing machine instructions, data, and programs.

- Program-controlled Input/Output operations.

# Instruction and Instruction Instruction Sequencing

#### "Must-Perform" Operations

- Data transfers between the memory and the processor registers

- Arithmetic and logic operations on data

- Program sequencing and control

- I/O transfers

#### Register Transfer Notation

- Identify a location by a symbolic name standing for its hardware binary address (LOC, R0,...)

- Contents of a location are denoted by placing square brackets around the name of the location (R1←[LOC], R3 ←[R1]+[R2])

- Register Transfer Notation (RTN)

#### **Assembly Language Notation**

- Represent machine instructions and programs.

- Move LOC, R1 = R1←[LOC]

- Add R1, R2, R3 = R3  $\leftarrow$  [R1]+[R2]

#### **CPU Organization**

- Single Accumulator

- Result usually goes to the Accumulator

- Accumulator has to be saved to memory quite often

- General Register

- Registers hold operands thus reduce memory traffic

- Register bookkeeping

- Stack

- Operands and result are always in the stack

- Three-Address Instructions

- ADD R1, R2, R3

$$R1 \leftarrow R2 + R3$$

- Two-Address Instructions

- ADD R1, R2

- One-Address Instructions

- ADD M

$$AC \leftarrow AC + M[AR]$$

- Zero-Address Instructions

- ADD

$$TOS \leftarrow TOS + (TOS - 1)$$

- RISC Instructions

- Lots of registers. Memory is restricted to Load & Store

Example: Evaluate (A+B) \* (C+D)

Three-Address

```

1. ADD R1, A, B ; R1 \leftarrow M[A] + M[B]

```

2. ADD R2, C, D ; R2

$$\leftarrow$$

M[C] + M[D]

3. MUL X, R1, R2 ;  $M[X] \leftarrow R1 * R2$

Example: Evaluate (A+B) \* (C+D)

Two-Address

;

$$R2 \leftarrow R2 + M[D]$$

Example: Evaluate (A+B) \* (C+D)

- One-Address

- 1. LOAD A

- 2. ADD B

- 3. STORET

- 4. LOAD C

- 5. ADD D

- 6. MUL T

- 7. STOREX

- ;  $AC \leftarrow M[A]$

- ;  $AC \leftarrow AC + M[B]$

- ; M[T] ← AC

- ;  $AC \leftarrow M[C]$

- ;  $AC \leftarrow AC + M[D]$

- ;  $AC \leftarrow AC * M[T]$

- ; M[X] ← AC

Example: Evaluate (A+B) \* (C+D)

- Zero-Address

- 1. PUSH A

- 2. PUSH B

- 3. ADD

- 4. PUSH C

- 5. PUSH D

- 6. ADD

- 7. MUL (C+D)\*(A+B)

- 8. POP X

; TOS ← A

; TOS ← B

; TOS  $\leftarrow$  (A + B)

; TOS ← C

; TOS ← D

; TOS  $\leftarrow$  (C + D)

: TOS ←

$M[X] \leftarrow TOS$

Example: Evaluate (A+B) \* (C+D)

#### RISC

- 1. LOAD R1, A

- 2. LOAD R2, B

- 3. LOAD R3, C

- 4. LOAD R4, D

- 5. ADD R1, R1, R2

- 6. ADD R3, R3, R4

- 7. MUL R1, R1, R3

- 8. STOREX, R1

; R1 ← M[A]

; R2 ← M[B]

; R3 ← M[C]

; R4  $\leftarrow$  M[D]

; R1 ← R1 + R2

; R3 ← R3 + R4

; R1 ← R1 \* R3

; M[X] ← R1

#### **Using Registers**

- Registers are faster

- Shorter instructions

- The number of registers is smaller (e.g. 32 registers need 5 bits)

- Potential speedup

- Minimize the frequency with which data is moved back and forth between the memory and processor registers.

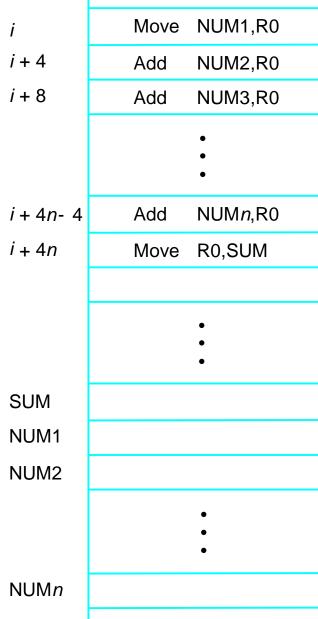

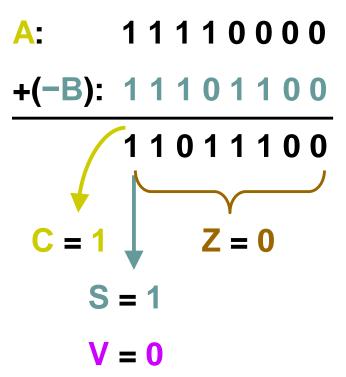

## Instruction Execution and Straight-Line Sequencing

Figure 2.8. A program for  $C \leftarrow [A] + [B]$ .

#### **Branching**

#### **Branching**

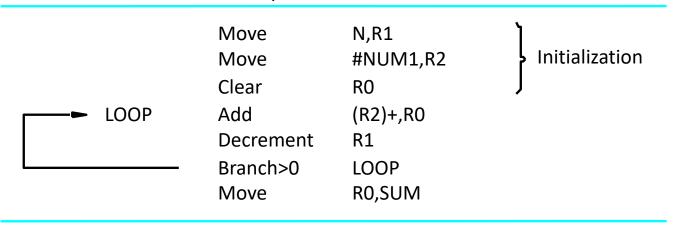

Program loop

LOOP

Move N,R1 Clear R0

Determine address of "Next" number and add "Next" number to R0

Decrement R1

Branch>0 LOOP

Move R0,SUM

•

n

NUM1

NUM2

SUM

Ν

Branch target

Conditional branch

Figure 2.10. Using a loop to add *n* numbers.

NUM*n*

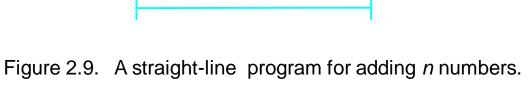

#### **Condition Codes**

- Condition code flags

- Condition code register / status register

- N (negative)

- Z (zero)

- V (overflow)

- C (carry)

- Different instructions affect different flags

### **Conditional Branch Instructions**

- Example:

- A: 11110000

- B: 00010100

#### **Status Bits** $C_{n-1}$ Α В $C_n$ F S $F_{n-1}$ **Zero Check**

#### THANK YOU

### COMPUTER ARCHITECTURE AND ORGANIZATION.

#### **UNIT-II**

Presented by Dr.K.RAJKAMAL, Assoc.Prof, Dept of ECE, KHIT.

#### **UNIT-II**

## Addressing Modes

#### **Generating Memory Addresses**

- How to specify the address of branch target?

- Can we give the memory operand address directly in a single Add instruction in the loop?

- Use a register to hold the address of NUM1; then increment by 4 on each pass through the loop.

- Implied

- AC is implied in "ADD M[AR]" in "One-Address" instr.

- TOS is implied in "ADD" in "Zero-Address" instr.

- Immediate

- The use of a constant in "MOV R1, 5", i.e. R1 ←

5

- Register

- Indicate which register holds the operand

- Register Indirect

- Indicate the register that holds the number of the register that holds the operand

MOV R1, (R2)

- Autoincrement / Autodecrement

- Access & update in 1 instr.

- Direct Address

- Use the given address to access a memory location

Indirect Address

Indicate the memory location that holds the address of the memory location that holds the data

$\overline{AR} = 101$ 100 101 102 103 104

Indexed

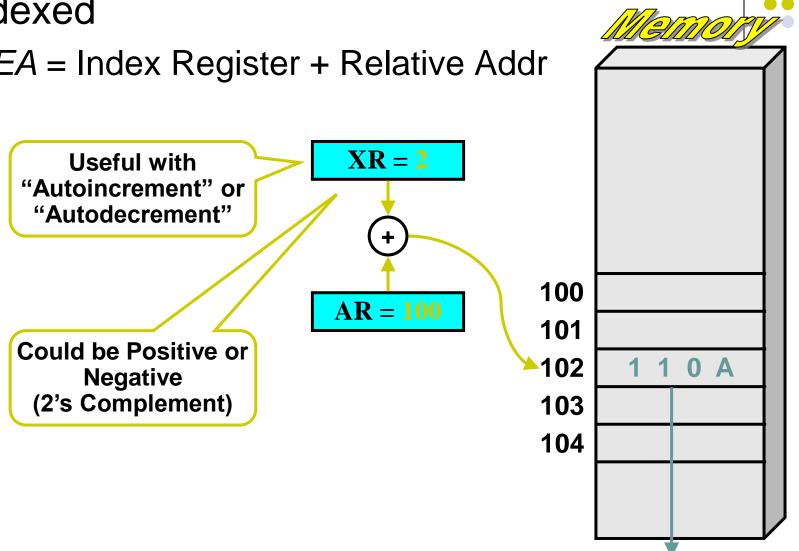

EA = Index Register + Relative Addr

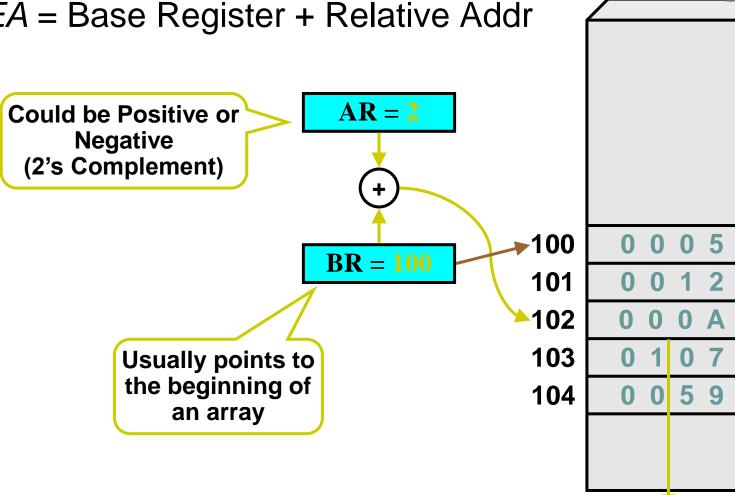

Base Register

EA = Base Register + Relative Addr

The different ways in which the location of an operand is specified in an instruction are referred to as addressing modes.

| Name                       | Assem bler syn tax         | Addressing function                          |

|----------------------------|----------------------------|----------------------------------------------|

| Immediate                  | #V alue                    | Op erand = Value                             |

| Register                   | R <i>i</i>                 | EA = Ri                                      |

| Absolute (Direct)          | LOC                        | EA = LOC                                     |

| Indirect                   | (R <i>i</i> )<br>(LOC)     | EA = [Ri] $EA = [LOC]$                       |

| Index                      | X(R <i>i</i> )             | EA = [Ri] + X                                |

| Base with index            | (R <i>i ,</i> R <i>j</i> ) | EA = [Ri] + [Rj]                             |

| Base with index and offset | X(R i,Rj)                  | EA = [Ri] + [Rj] + X                         |

| Relative                   | X(PC)                      | EA = [PC] + X                                |

| Autoincremen t             | (R <i>i</i> )+             | EA = [R <i>i</i> ];<br>Incremen t R <i>i</i> |

| Autodecrement              | -(R <i>i</i> )             | Decremen t R $i$ ;<br>EA = [R $i$ ]          |

#### **Indexing and Arrays**

- Index mode the effective address of the operand is generated by adding a constant value to the contents of a register.

- Index register

- $X(R_i)$ :  $EA = X + [R_i]$

- The constant X may be given either as an explicit number or as a symbolic name representing a numerical value.

- If X is shorter than a word, sign-extension is needed.

#### **Indexing and Arrays**

- In general, the Index mode facilitates access to an operand whose location is defined relative to a reference point within the data structure in which the operand appears.

- Several variations:

$$(R_i, R_j)$$

: EA =  $[R_i]$  +  $[R_j]$

$X(R_i, R_i)$ : EA =  $X$  +  $[R_i]$  +  $[R_i]$

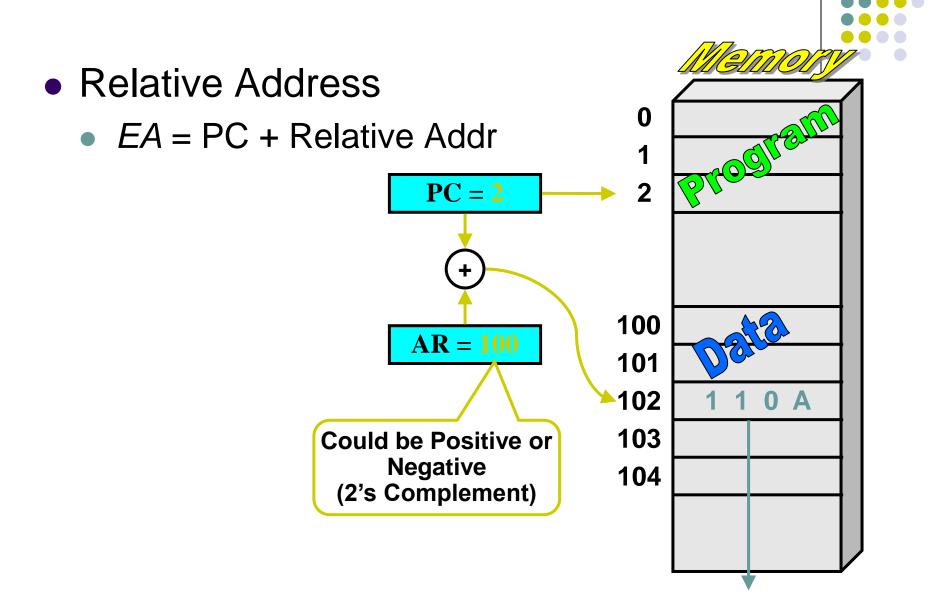

#### Relative Addressing

- Relative mode the effective address is determined by the Index mode using the program counter in place of the general-purpose register.

- X(PC) note that X is a signed number

- Branch>0 LOOP

- This location is computed by specifying it as an offset from the current value of PC.

- Branch target may be either before or after the branch instruction, the offset is given as a singed num.

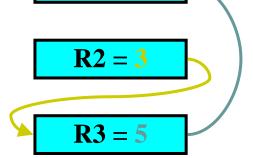

- Autoincrement mode the effective address of the operand is the contents of a register specified in the instruction. After accessing the operand, the contents of this register are automatically incremented to point to the next item in a list.

- (R<sub>i</sub>)+. The increment is 1 for byte-sized operands, 2 for 16-bit operands, and 4 for 32-bit operands.

- Autodecrement mode: -(R<sub>i</sub>) decrement first

Figure 2.16. The Autoincrement addressing mode used in the program of Figure 2.12.

# Basic Input / Output Operations

#### 1/0

- The data on which the instructions operate are not necessarily already stored in memory.

- Data need to be transferred between processor and outside world (disk, keyboard, etc.)

- I/O operations are essential, the way they are performed can have a significant effect on the performance of the computer.

- Read in character input from a keyboard and produce character output on a display screen.

- Rate of data transfer (keyboard, display, processor)

- Difference in speed between processor and I/O device creates the need for mechanisms to synchronize the transfer of data.

- A solution: on output, the processor sends the first character and then waits for a signal from the display that the character has been received. It then sends the second character. Input is sent from the keyboard in a similar way.

- Registers

- Flags

- Device interface

Machine instructions that can check the state

of the status flags and transfer data:

READWAIT Branch to READWAIT if SIN = 0

Input from DATAIN to R1

WRITEWAIT Branch to WRITEWAIT if SOUT = 0

Output from R1 to DATAOUT

Memory-Mapped I/O – some memory address values are used to refer to peripheral device buffer registers. No special instructions are needed. Also use device status registers.

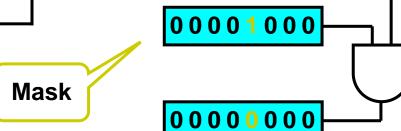

READWAIT Testbit #3, INSTATUS

Branch=0 READWAIT

MoveByte DATAIN, R1

- Assumption the initial state of SIN is 0 and the initial state of SOUT is 1.

- Any drawback of this mechanism in terms of efficiency?

- Two wait loops > processor execution time is wasted

- Alternate solution?

- Interrupt

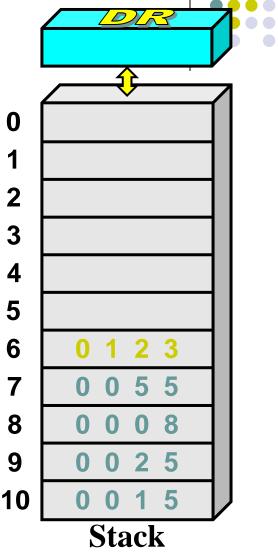

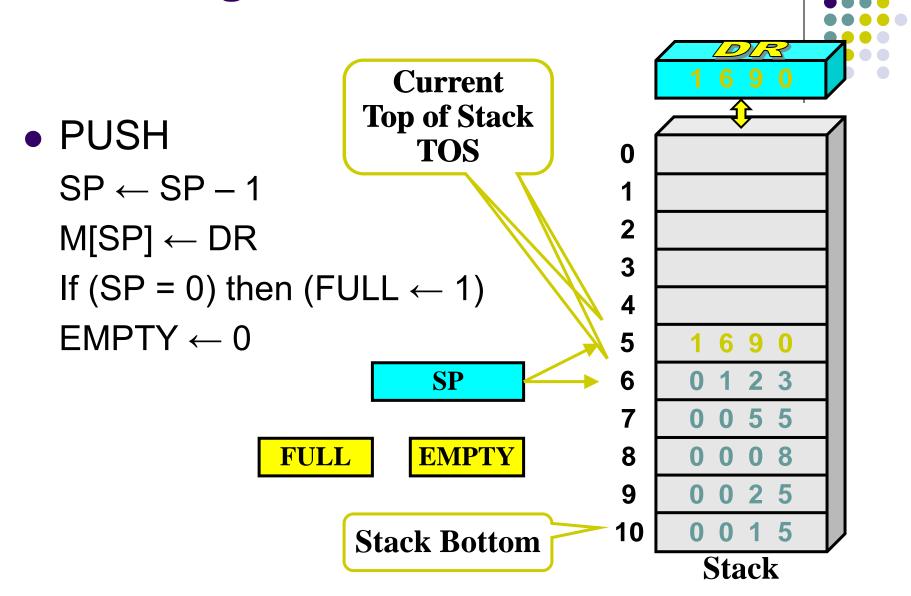

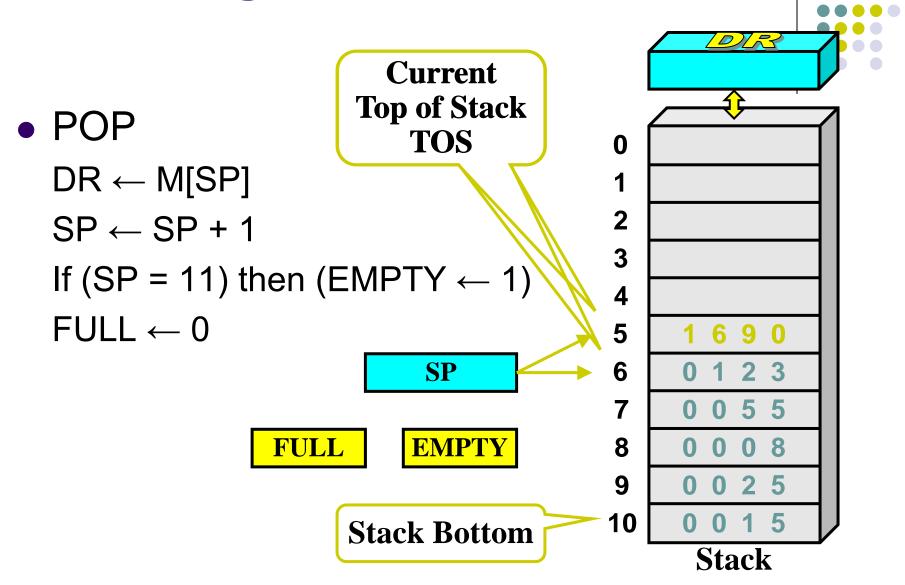

## Stacks & Queues

• LIFO

Last In First Out

Current

Top of Stack

TOS

1

2

3

4

5

6

0

**FULL**

**EMPTY**

**Stack Bottom**

- Memory Stack

- PUSH

$$SP \leftarrow SP - 1$$

M[SP]  $\leftarrow$  DR

POP

$$DR \leftarrow M[SP]$$

$SP \leftarrow SP + 1$

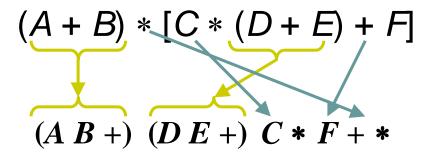

#### **Reverse Polish Notation**

Infix Notation

$$A + B$$

Prefix or Polish Notation

$$+AB$$

Postfix or Reverse Polish Notation (RPN)

$$AB+$$

$$A * B + C * D$$

$\longrightarrow$   $A B * C D * +$

#### **Reverse Polish Notation**

Example

#### **Reverse Polish Notation**

Stack Operation

$$(3)(4)*(5)(6)*+$$

PUSH 3

PUSH 4

**MULT**

PUSH 5

PUSH 6

**MULT**

**ADD**

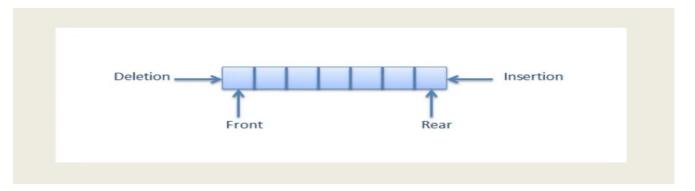

#### Queues

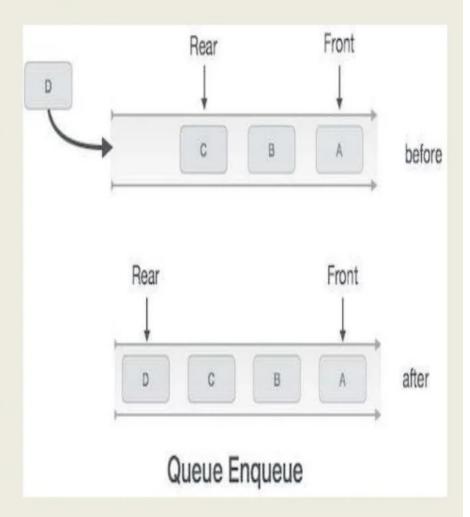

- Queue is an ADT data structure similar to stack, except that the first item to be inserted is the first one to be removed.

- This mechanism is called First-In-First-Out (FIFO).

- Placing an item in a queue is called "insertion or enqueue", which is done at the end of the queue called "rear".

- Removing an item from a queue is called "deletion or dequeue", which is done at the other end of the queue called "front".

- Some of the applications are : printer queue, keystroke queue, etc.

#### The Queue Operation

Placing an item in a queue is called "insertion or enqueue", which is done at the end of the queue called "rear".

## Operations On A Queue

- 1.To insert an element in queue

- 2.Delete an element from queue

#### <u>Algorithm QINSERT (ITEM)</u>

```

1.If (rear = maxsize-1)

print ("queue overflow") and return

2.Else

rear = rear + 1

Queue [rear] = item

```

#### Algorithm QDELETE ()

```

1.If (front = rear)

print "queue empty" and return

```

#### 2. Else

```

Front = front + 1

item = queue [front];

Return item

```

## Queue Applications

- Real life examples

- √Waiting in line

- √Waiting on hold for tech support

- Applications related to Computer Science

- √ Round robin scheduling

- ✓ Job scheduling (FIFO Scheduling)

- √Key board buffer

#### 3 states of the queue

- 1.Queue is empty

- FRONT=REAR

- 2.Queue is full

- REAR=N

- 3.Queue contains element >=1

FRONT<REAR

NO. OF ELEMENT=REAR-FRONT+1

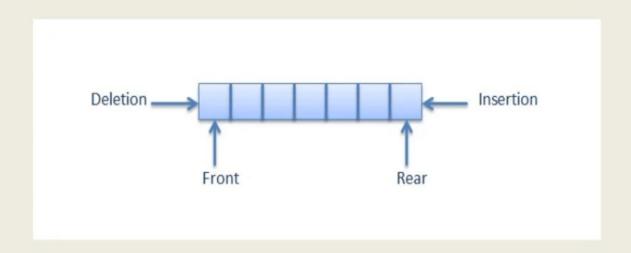

## Type of queue

Simple Queue

Circular Queue

Priority Queue Dequeue (Double ended Queue)

## Simple Queue

• Simple queue defines the simple operation of queue in which insertion occurs at the rear of the list and deletion occurs at the front of the list.

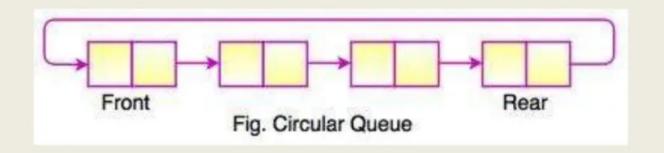

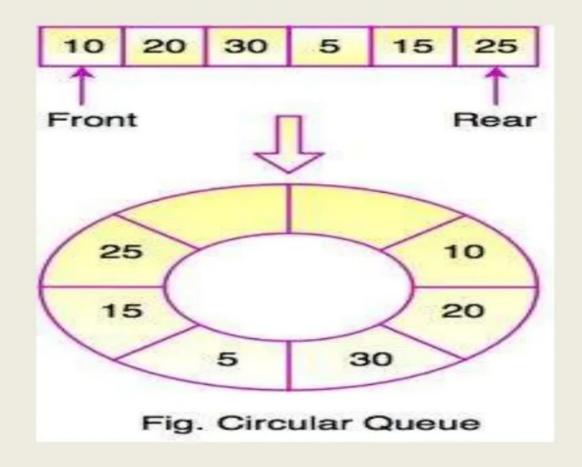

# Circular Queue

- In a circular queue, all nodes are treated as circular. Last node is connected back to the first node.

- Circular queue is also called as Ring Buffer.

- It is an abstract data type.

- Circular queue contains a collection of data which allows insertion of data at the end of the queue and deletion of data at the beginning of the queue

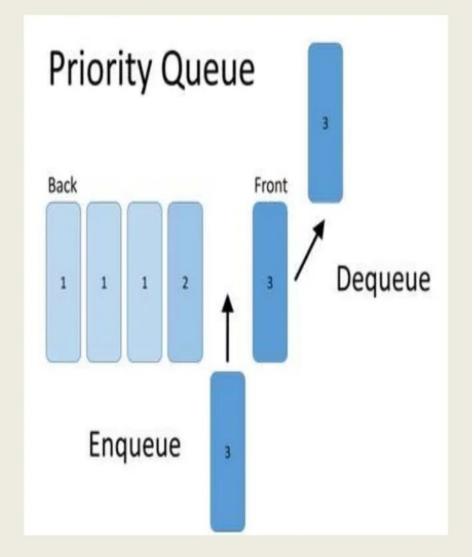

# **Priority Queue**

- Priority queue contains data items which have some preset priority. While removing an element from a priority queue, the data item with the highest priority is removed first.

- In a priority queue, insertion is performed in the order of arrival and deletion is performed based on the priority.

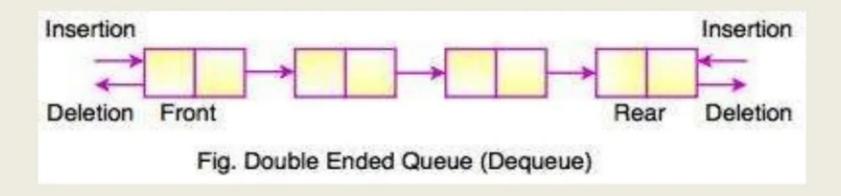

# Dequeue (Double ended Queue)

In Double Ended Queue, insert and delete operation can be occur at both ends that is front and rear of the queue

# **Enqueue Operation**

- Step 1 Check if the queue is full.

- Step 2 If the queue is full, produce overflow error and exit.

- Step 3 If the queue is not full, increment rear pointer to point the next empty space.

- Step 4 Add data element to the queue location, where the rear is pointing.

- Step 5 return success.

# Dequeue Operation

- Step 1 Check if the queue is empty.

- Step 2 If the queue is empty, produce underflow error and exit.

- Step 3 If the queue is not empty, access the data where front is pointing.

- Step 4 –

Increment front pointer to point to the next available data element.

- Step 5 Return success.

# **Component of Instructions**

Logic Instructions, shift and Rotate Instructions

**Additional Instructions**

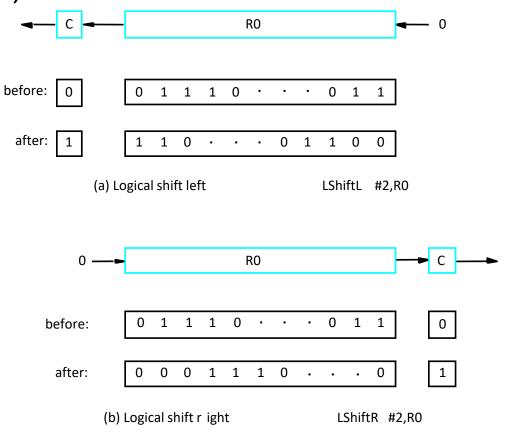

Logical shift – shifting left (LShiftL) and shifting right (LShiftR)

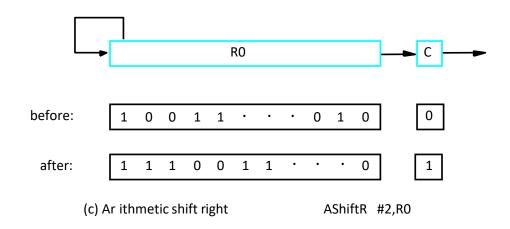

## **Arithmetic Shifts**

#### Rotate

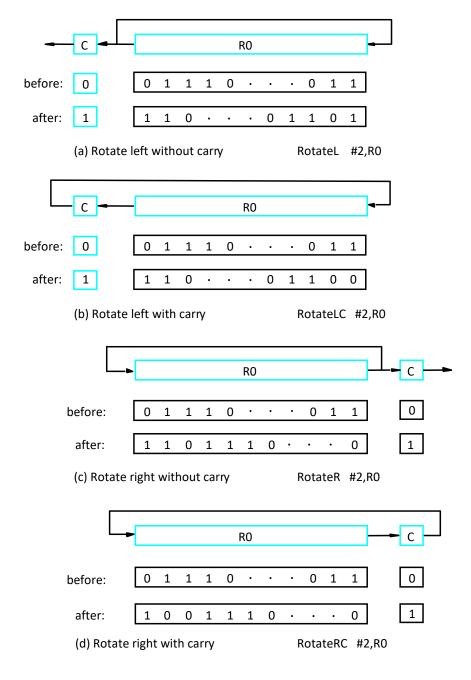

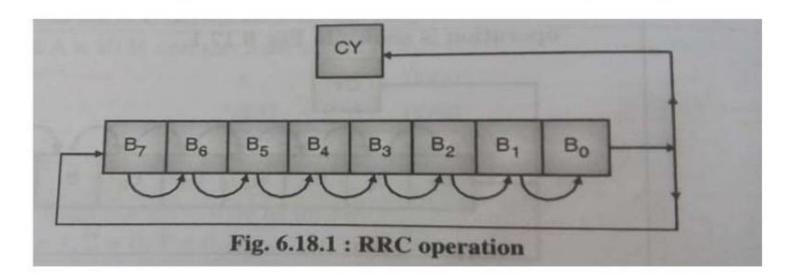

Figure 2.32. Rotate instructions.

## Rotate

Each bit in the accumulator can be shifted either left or right to the next position.

| Opcode | Operand | Description             |

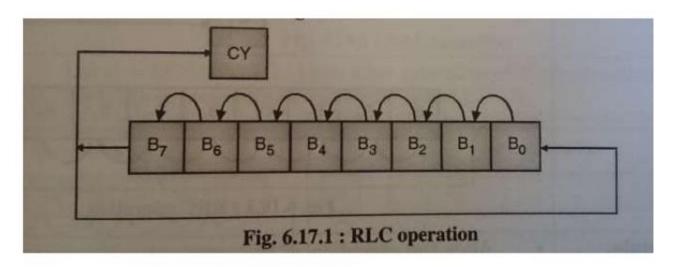

|--------|---------|-------------------------|

| RLC    | None    | Rotate accumulator left |

Each binary bit of the accumulator is rotated left by one position.

- Bit D7 is placed in the position of D0 as well as in the Carry flag.

- CY is modified according to bit D7.

- S, Z, P, AC are not affected.

Example: RLC.

| Opcode | Operand | Description              |  |

|--------|---------|--------------------------|--|

| RRC    | None    | Rotate accumulator right |  |

- Each binary bit of the accumulator is rotated right by one position.

- ➤ Bit D0 is placed in the position of D7 as well as in the Carry flag.

- >CY is modified according to bit D0.

- ➤S, Z, P, AC are not affected.

#### Example: RRC.

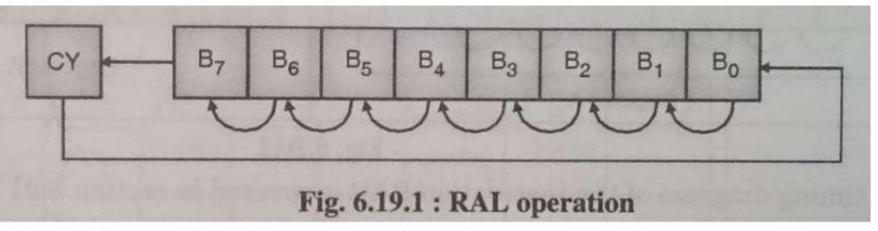

| Opcode | Operand | Description                           |

|--------|---------|---------------------------------------|

| RAL    | None    | Rotate accumulator left through carry |

- Each binary bit of the accumulator is rotated left by one position through the Carry flag.

- ➤ Bit D7 is placed in the Carry flag, and the Carry flag is placed in the least significant position D0.

- ➤ CY is modified according to bit D7.

- > S, Z, P, AC are not affected.

#### **Example: RAL.**

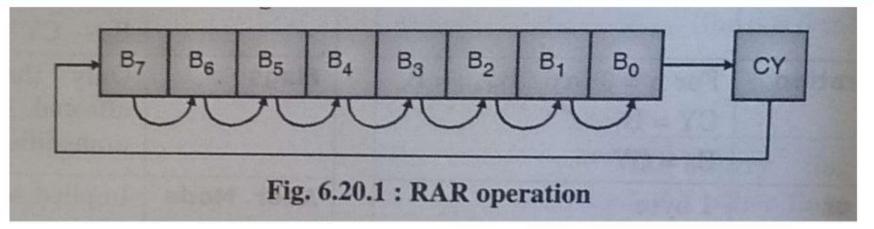

| Opcode | Operand | Description                            |

|--------|---------|----------------------------------------|

| RAR    | None    | Rotate accumulator right through carry |

- Each binary bit of the accumulator is rotated right by one position through the Carry flag.

- ➤ Bit D0 is placed in the Carry flag, and the Carry flag is placed in the most significant position D7.

- ➤ CY is modified according to bit D0.

- >S, Z, P, AC are not affected.

Example: RAR.

# Complement

- The contents of accumulator can be complemented.

- ▶ Each 0 is replaced by 1 and each 1 is replaced by 0.

| Opcode | Operand | Description            |

|--------|---------|------------------------|

| СМА    | None    | Complement accumulator |

- > The contents of the accumulator are complemented.

- ➤ No flags are affected.

Example: CMA.

| Opcode | Operand | Description      | 2 |

|--------|---------|------------------|---|

| CMC    | None    | Complement carry |   |

- ➤ The Carry flag is complemented.

- No other flags are affected.

- **Example:** CMC.

| Opcode | Operand | Description |

|--------|---------|-------------|

| STC    | None    | Set carry   |

- The Carry flag is set to 1.

- ➤ No other flags are affected.

- **Example: STC.**

# **Multiplication and Division**

- Not very popular (especially division)

- Multiply  $R_i$ ,  $R_j$  $R_j \leftarrow [R_i] \times [R_j]$

- 2n-bit product case: high-order half in R(j+1)

- Divide R<sub>i</sub>, R<sub>j</sub>

R<sub>j</sub> ← [R<sub>i</sub>] / [R<sub>j</sub>]

Quotient is in R<sub>j</sub>, remainder may be placed in R(j+1)

Arithmetic and Logic Instructions, Branch Instructions

# **Types of Instructions**

Data Transfer Instructions

| Name     | Mnemonic |

|----------|----------|

| Load     | LD       |

| Store    | ST       |

| Move     | MOV      |

| Exchange | XCH      |

| Input    | IN       |

| Output   | OUT      |

| Push     | PUSH     |

| Pop      | POP      |

### **Data Transfer Instructions**

| Mode              | Assembly  | Register Transfer                         |

|-------------------|-----------|-------------------------------------------|

| Direct address    | LD ADR    | $AC \leftarrow M[ADR]$                    |

| Indirect address  | LD @ADR   | $AC \leftarrow M[M[ADR]]$                 |

| Relative address  | LD \$ADR  | $AC \leftarrow M[PC + ADR]$               |

| Immediate operand | LD #NBR   | AC ← NBR                                  |

| Index addressing  | LD ADR(X) | $AC \leftarrow M[ADR + XR]$               |

| Register          | LD R1     | AC ← R1                                   |

| Register indirect | LD (R1)   | $AC \leftarrow M[R1]$                     |

| Autoincrement     | LD (R1)+  | $AC \leftarrow M[R1], R1 \leftarrow R1+1$ |

# **Data Manipulation Instructions**

- Arithmetic

- Logical & Bit Manipulation

- Shift

| Name              | Mnemonic |

|-------------------|----------|

| Clear             | CLR      |

| Complement        | COM      |

| AND               | AND      |

| OR                | OR       |

| Exclusive-OR      | XOR      |

| Clear carry       | CLRC     |

| Set carry         | SETC     |

| Complement carry  | COMC     |

| Enable interrupt  | EI       |

| Disable interrupt | DI       |

| Name                 | Mnemonic |

|----------------------|----------|

| Increment            | INC      |

| Decrement            | DEC      |

| Add                  | ADD      |

| Subtract             | SUB      |

| Multiply             | MUL      |

| Divide               | DIV      |

| Add with carry       | ADDC     |

| Subtract with borrow | SUBB     |

| Maria                | AIE C    |

| Name                       | Mnemonic |

|----------------------------|----------|

| Logical shift right        | SHR      |

| Logical shift left         | SHL      |

| Arithmetic shift right     | SHRA     |

| Arithmetic shift left      | SHLA     |

| Rotate right               | ROR      |

| Rotate left                | ROL      |

| Rotate right through carry | RORC     |

| Rotate left through carry  | ROLC     |

# **Program Control Instructions**

| Name                  | Mnemonic |

|-----------------------|----------|

| Branch                | BR       |

| Jump                  | JMP      |

| Skip                  | SKP      |

| Call                  | CALL     |

| Return                | RET      |

| Compare<br>(Subtract) | CMP      |

| Test (AND)            | TST      |

Subtract A – B but don't store the result

10110001

# **Conditional Branch Instructions**

| Mnemonic | Branch Condition      | <b>Tested Condition</b> |

|----------|-----------------------|-------------------------|

| BZ       | Branch if zero        | Z = 1                   |

| BNZ      | Branch if not zero    | Z = 0                   |

| BC       | Branch if carry       | C = 1                   |

| BNC      | Branch if no carry    | C = 0                   |

| BP       | Branch if plus        | S = 0                   |

| BM       | Branch if minus       | S = 1                   |

| BV       | Branch if overflow    | V = 1                   |

| BNV      | Branch if no overflow | V = 0                   |

# Thank you

### **UNIT-III**

#### INPUT/OUTPUT ORGANIZATION

# I/O Organization

The Input / output organization of computer depends upon the size of computer and the peripherals connected to it. The I/O Subsystem of the computer, provides an efficient mode of communication between the central system and the outside environment.

# Peripheral Devices

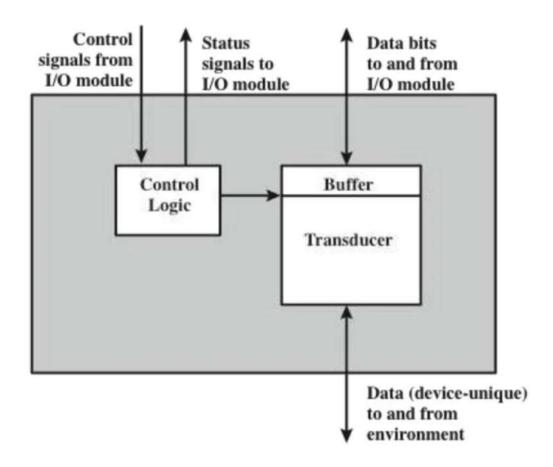

An external device connected to an I/O module Provide a means of exchanging data between the external device environment and the computer.

Attach to the computer by a link to an I/O module

The link is used to exchange control, status, and data between the I/O module and the external device.

# Peripheral Devices

#### The most common input output devices are:

- i) Monitor

- ii) Keyboard

- iii) Mouse

- iv) Printer

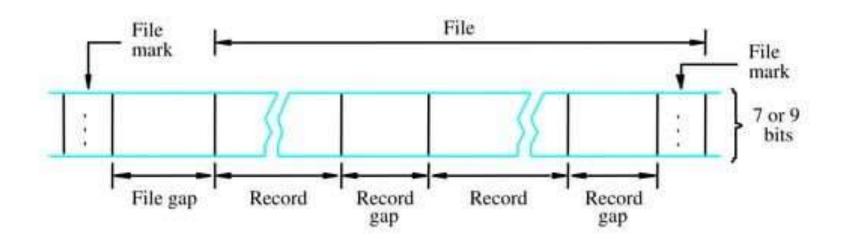

- v) Magnetic tapes

The devices that are under the direct control of the computer are said to be connected online.

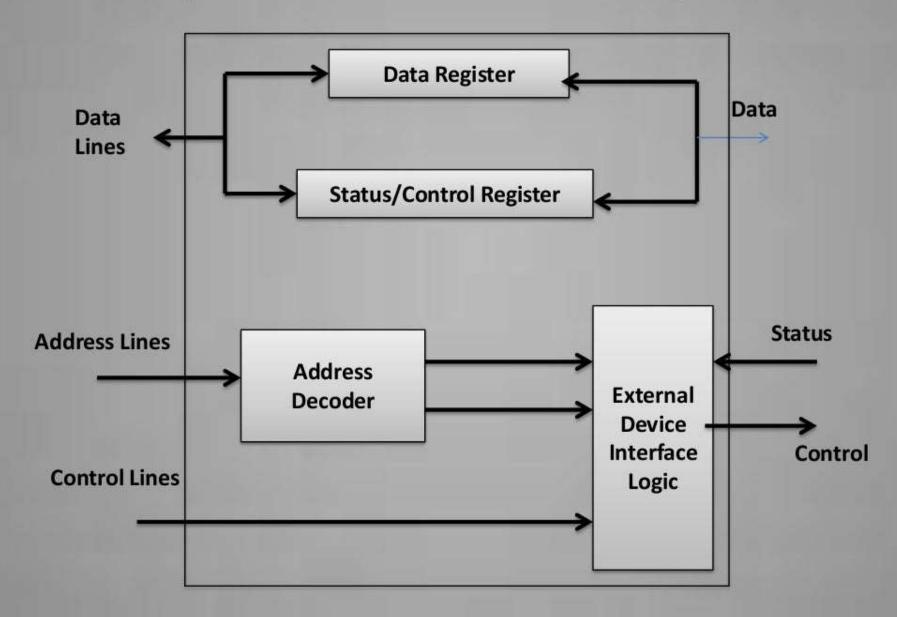

Figure 7.2 Block Diagram of an External Device

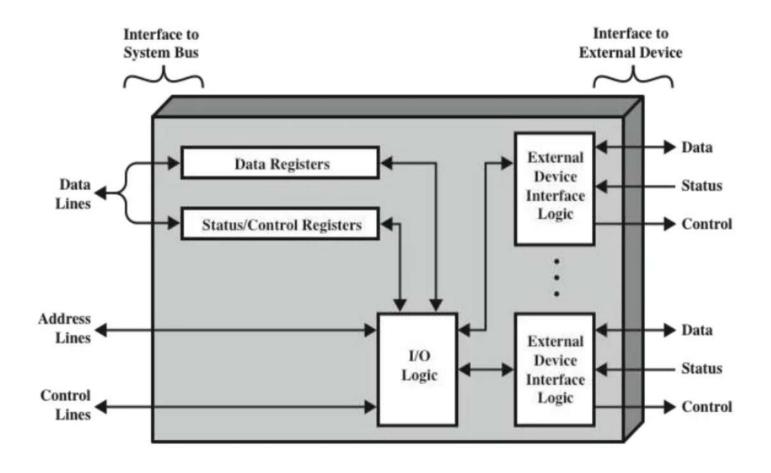

# I/O Module Structure

Figure 7.3 Block Diagram of an I/O Module

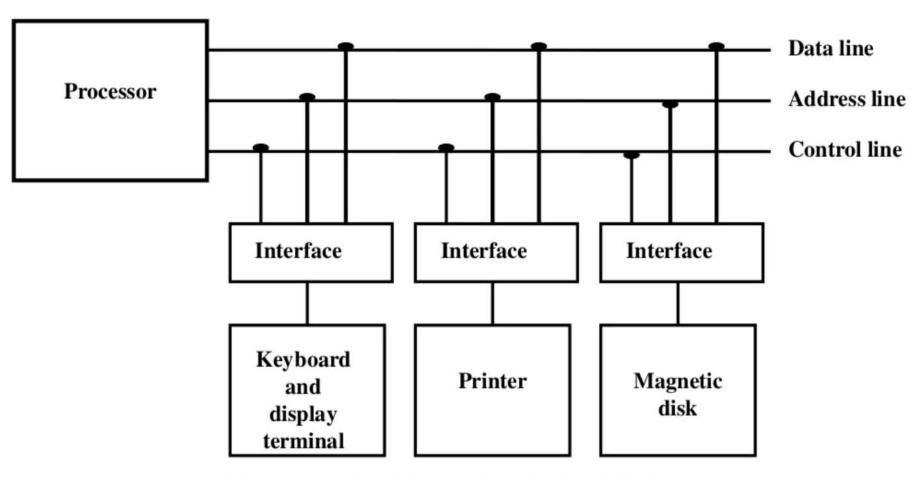

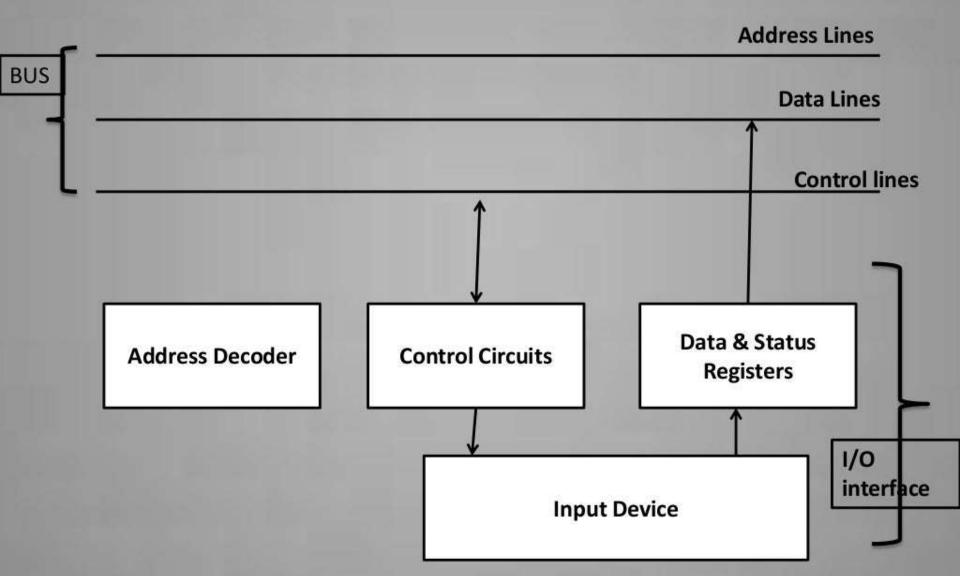

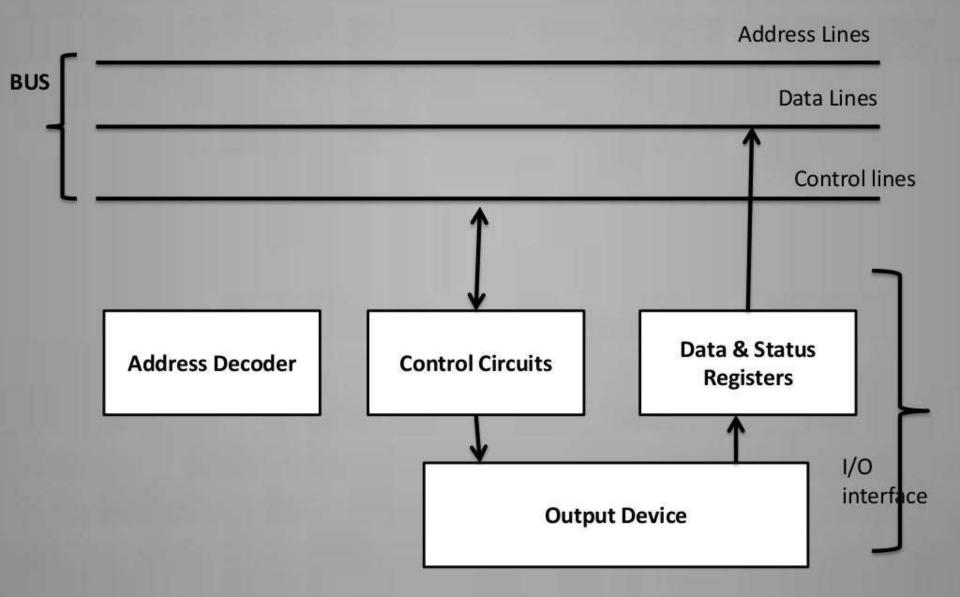

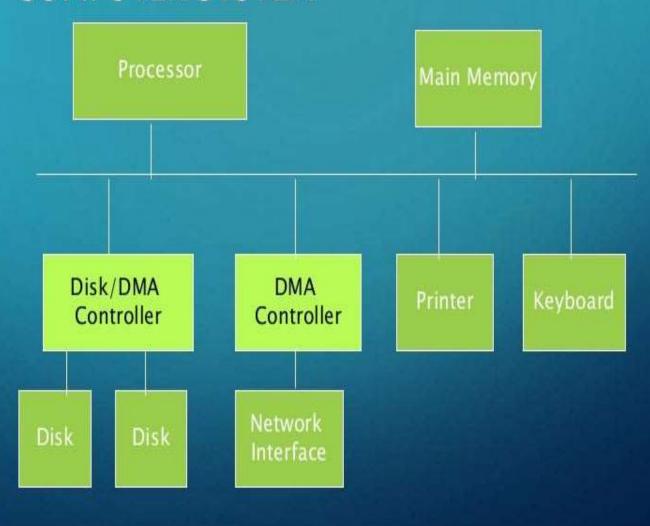

# I/O BUS and Interface Module

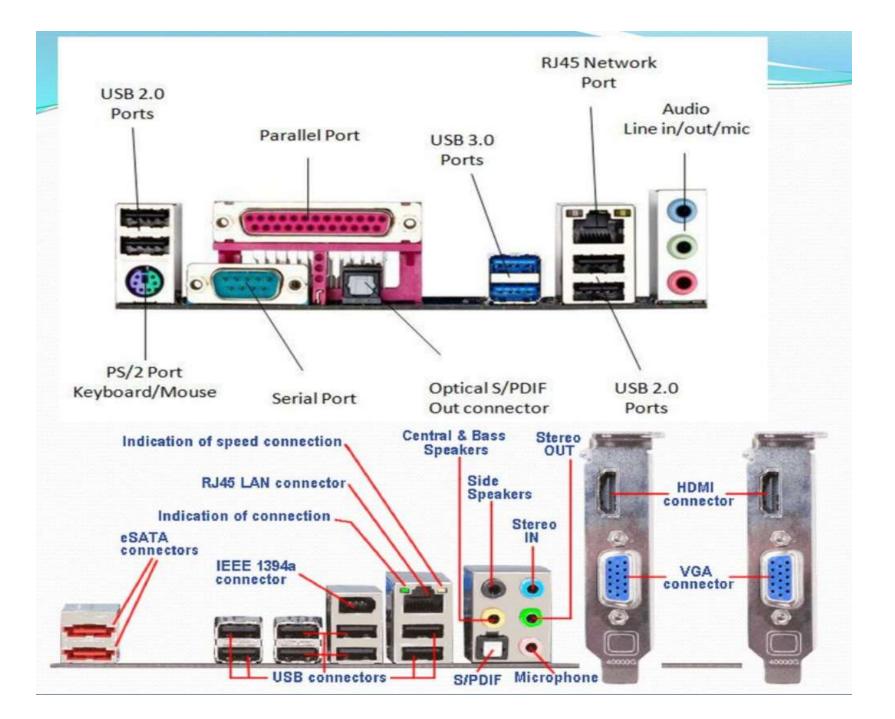

It defines the typical link between the processor and several peripherals. The I/O Bus consists of data lines, address lines and control lines.

# I/O BUS and Interface Module

Connection of I/O bus to input-output devices

#### I/O Commands

There are four types of I/O commands that an I/O module may receive when it is addressed by a processor:

#### **Control**

used to activate a peripheral and tell it what to do.

#### <u>Test</u>

used to test various status conditions associated with an I/O module and its peripherals.

#### Read

causes the I/O module to obtain an item of data from the peripheral and place it in an internal buffer.

#### <u>Write</u>

causes the I/O module to take an item of data from the data bus and subsequently transmit that data item to the peripheral.

# Accessing I/O Devices

- I/O devices accessed through I/O interface.

- Requirements for I/O interface:

- CPU communication

- Device communication

- Data buffering

- Control and timing

- Error detection.

#### **CPU Communication:**

- Processor sends commands to the I/O system which are generally the control signals on the control bus.

- Exchange of data between the processor and the I/O interface over the data bus.

- Check whether the devices are ready or not.

#### **Data Buffering:**

- Data transfer rate is too high.

- Data from processor and memory are sent to an I/O interface, buffered and then sent to the peripheral device at its data rate.

#### **Error Detection:**

- I/O interface is responsible for error detection

- Used to report errors to the processor.

- Types of errors:

- Mechanical, electrical malfunctions, bad disk track, unintentional changes.

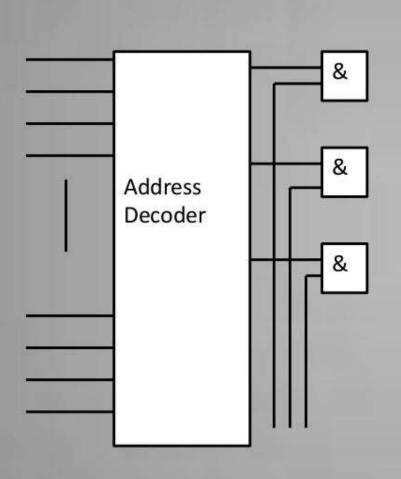

### I/O interface Block diagram

- <u>Data Register:</u> holds the data being transferred to or from the processor.

- <u>Status/Control</u> <u>Register:</u> contains information relevant to the operation.

- Data and status/control registers: are connected to the data bus.

- Address decoder: enables the device to recognize its address.

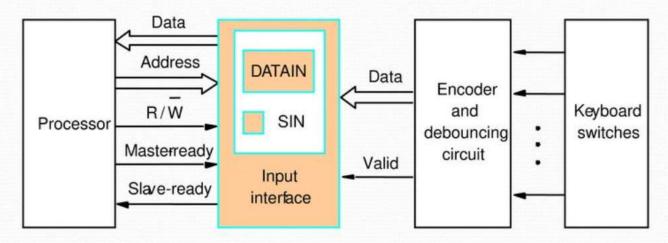

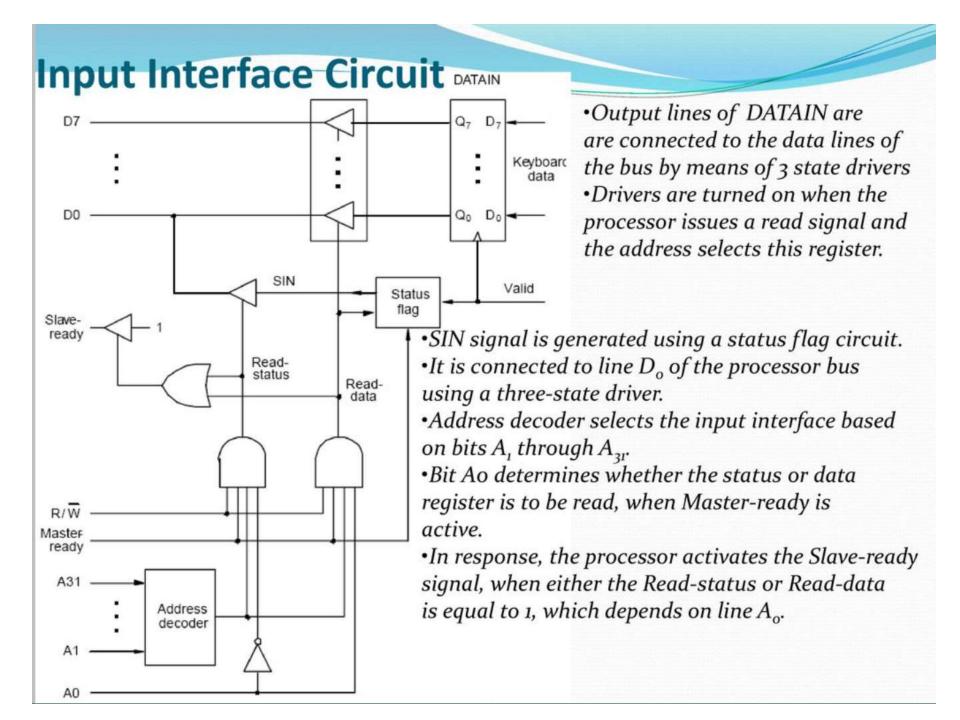

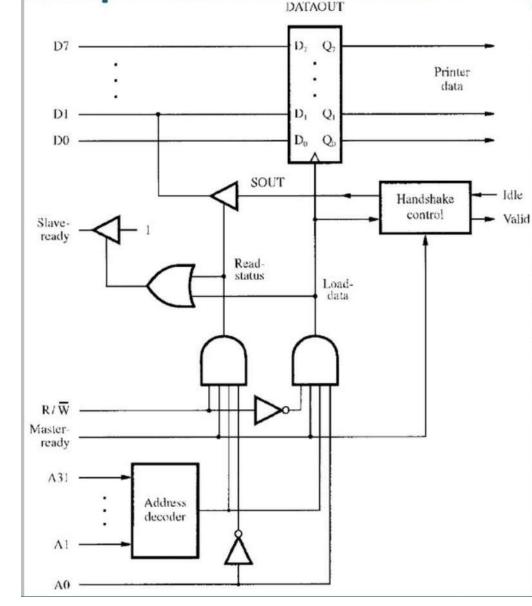

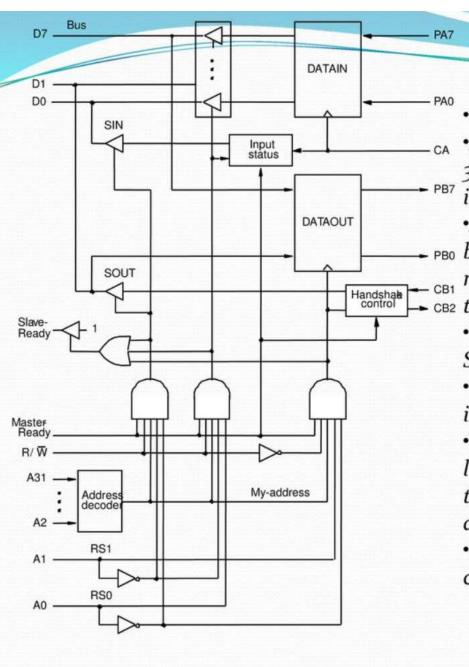

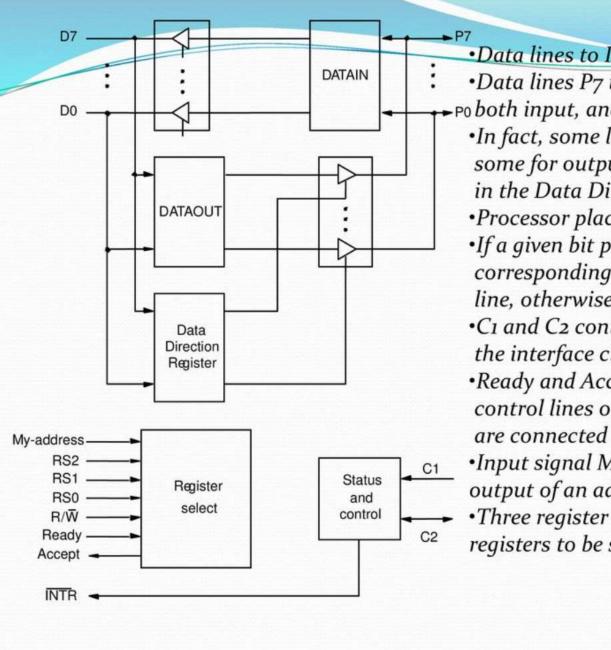

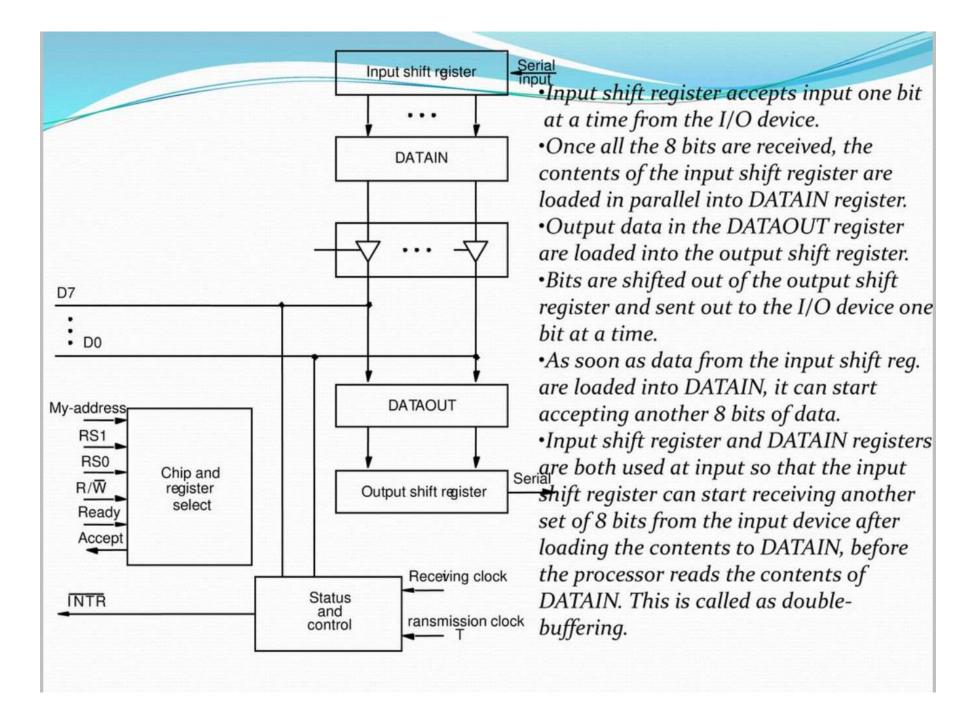

# I/O interface for Input Device

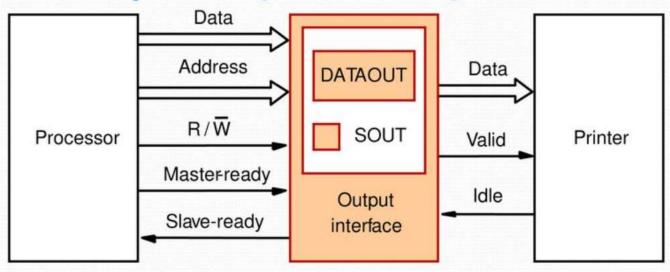

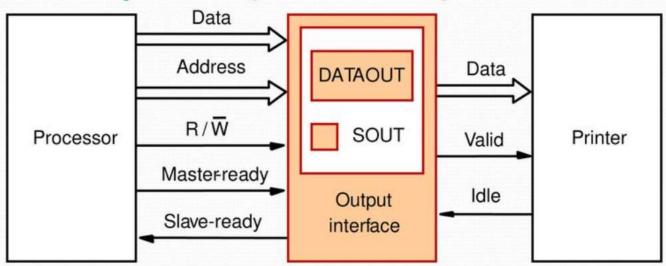

# I/O interface for Output Device

# I/O interface Techniques

# I/O Ports

- 4 registers status, control, data-in, data-out

- Status states whether the current command is completed, byte is available, device has an error, etc

- Control host determines to start a command or change the mode of a device

- Data-in host reads to get input

- Data-out host writes to send output

- Size of registers 1 to 4 bytes

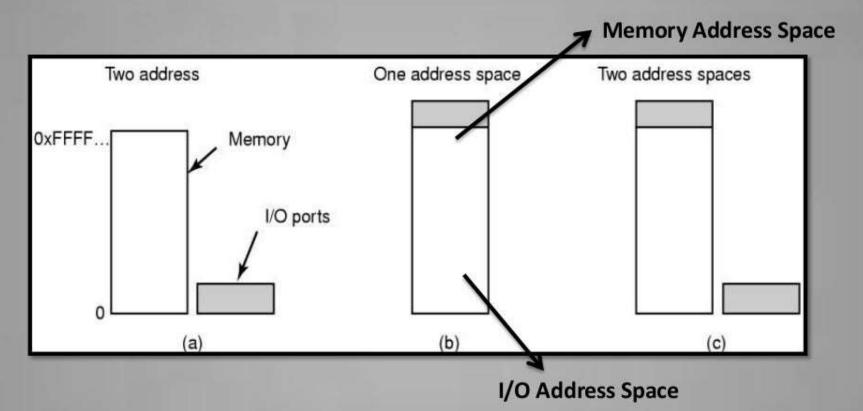

# I/O devices can be interfaced to a computer system I/O in 2 ways:

- Memory Mapped I/O

- I/O mapped I/O

# Memory-Mapped I/O (1)

- (a) Separate I/O and memory space

- (b) Memory-mapped I/O

- (c) Hybrid

# Memory Mapped I/O

- No need of special I/O instructions.

- Memory related instructions are used for I/O related operations.

# I/O Mapped I/O

Memory Address

Space

Total Address Space

I/O address Space

# I/O Mapped I/O

- If we want to reduce the memory address space, we allot a different I/O address space, apart from total memory space.

- **➤ Memory related instructions do not work here**

- ➤ Processor use these mode only for I/O Read, I/O Write.

# Difference between Memory Mapped I/O & I/O mapped I/O

| Memory Mapped I/O                                                  | I/O Mapped I/O                                                         |

|--------------------------------------------------------------------|------------------------------------------------------------------------|

| Memory & I/O share the entire address range of processor           | Processor provides separate address range for memory & I/O             |

| Processor provides more address lines for accessing memory         | Less address lines for accessing I/O                                   |

| More Decoding is required                                          | Less decoding is required                                              |

| Memory control signals used to control Read & Write I/O operations | I/O control signals are used to control<br>Read & Write I/O operations |

# Programmed I/O

- I/O operation means

- A data transfer between an I/O device & memory or

- Between I/O device & Processor.

- If any I/O operations are completely controlled by processor, then the system is said to be using "Programmed I/O"

- Processor has to check I/O system periodically until the operation completes → "POLLING"

- Microprocessor has to check if any device need service.

# Programmed I/O

#### **Priority:**

- ➤ The Routines assigns priority to the different I/O devices

- ➤ Port A is always checked 1<sup>st</sup>.

- > Then Port B

- > Then Port C

- Order may change by changing routine.

# INTERRUPTS

#### INTRODUCTION

- INTERRUPT meaning to break the sequence of operations.

- While the processor is executing a program an 'interrupt' breaks the sequence of execution of that program and start execution of another program.

#### **INTERRUPT**

Interrupt is a signal from a device attached to a computer or from a program within the computer that requires the operating system to figure out what to do next.

# Need of Interrupts?

- Devices and programs occasionally need CPU service but we can't predict when.

- So for the interaction with CPU each device or a program is allowed to give interrupt so that it can be used as a signal to the processor.

- Need a way for CPU to find out devices/programs need attention

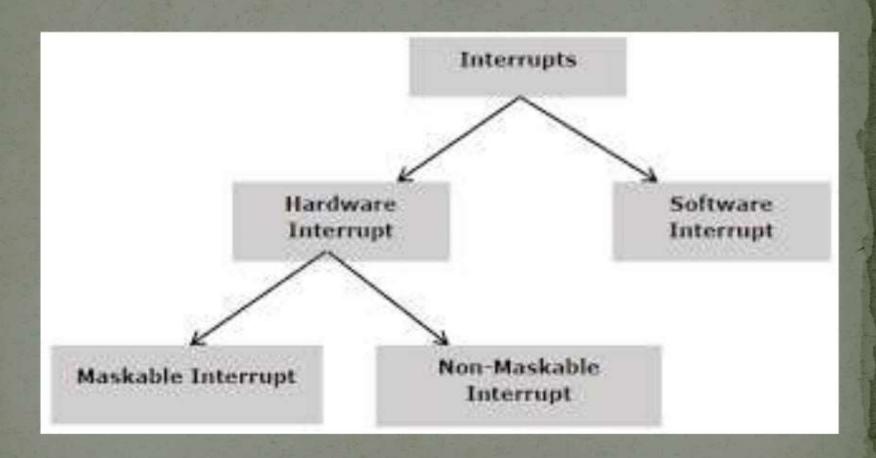

# **Types of Interrupts**

Generally Interrupts are of Two types.

- Hardware Interrupts

- 2) Software Interrupts

# **Types**

# Hardware Interrupt

If the signal for the processor is from external device or hardware it is called hardware interrupts.

#### Example:

Keystroke(pressing of key on keyboard) and mouse movements cause hardware interrupts.

# **Hardware Interrupt**

#### Mask-able Interrupt:

The hardware interrupts which can be delayed when a much highest priority interrupt has occurred to the processor.

#### Non Mask-able Interrupt:

The hardware which cannot be delayed and should process by the processor immediately.

#### 4.2 INTERRUPTS

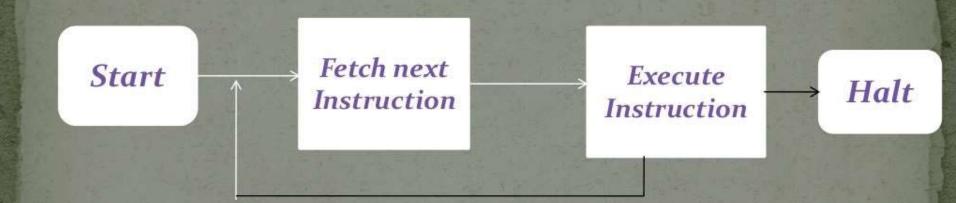

# **Instruction Cycle**

- ➤ An instruction cycle includes

- Fetch

- Decode

- Execute

- ➤ It is the basic operation cycle of a computer. It is the process by which a computer retrieves a program instruction from its memory, determines what actions the instruction requires, and carries out those actions. This cycle is repeated continuously by the central processing unit (CPU).

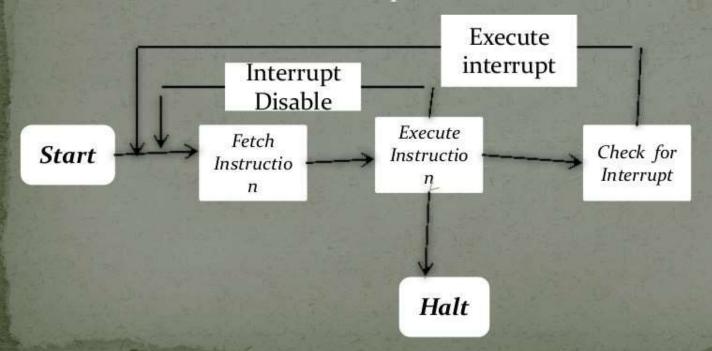

# Instruction Cycle and Interrupts

#### Without Interrupts

- Instruction fetch

- Instruction execute

# Instruction cycle and Interrupts

#### With Interrupt

Instruction Fetch

Instruction Execute

Check the Interrupt

# Classes of Interrupt

#### **Program**

Generated by some condition that occurs as a result of an instruction execution, such as arithmetic overflow, division by zero, attempt to execute an illegal machine instruction, and reference outside a user's allowed memory space

#### >Timer

Generated by a timer within the processor. This allows the operating system to perform certain functions on a regular basis.

#### >I/O

Generated by an I/O controller, to signal normal completion of an operation or to signal a variety of error conditions.

#### > Hardware Failure

Generated by a failure, such as power failure or memory parity error.

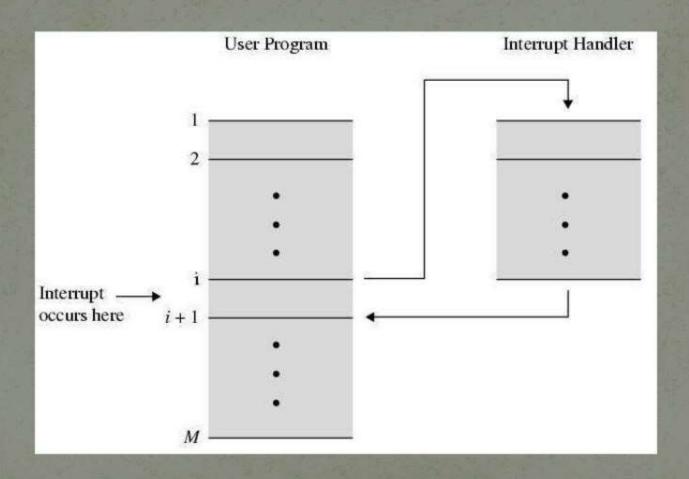

# How Interrupts are handled?

- If there is an interrupt in instruction cycle then

- It will trigger the interrupt handler.

- The handler will stop the present instruction which is processing and save its state in a PC register and load the state of the interrupt program.

- OS serves the interrupt from Interrupt Vector Table through Interrupt Service Routine(Interrupt handler).

- After processing the interrupt, interrupt handler will load the

instruction of previous saved process from the register, process will

start its processing where it's left. This saving the old instruction

processing configuration and loading the new interrupt configuration

is also called as context switching.

# Interrupt Handling

# Multiple Interrupts

An interrupt event that can occur while the processor is handling a previous interrupt.

#### ✓ Disable Interrupt:

Processor Will ignore further interrupts while handling one interrupt (Sequential Interrupt)

#### ✓ Define Priorities:

Low priority interrupt interrupted by higher priority interrupts.

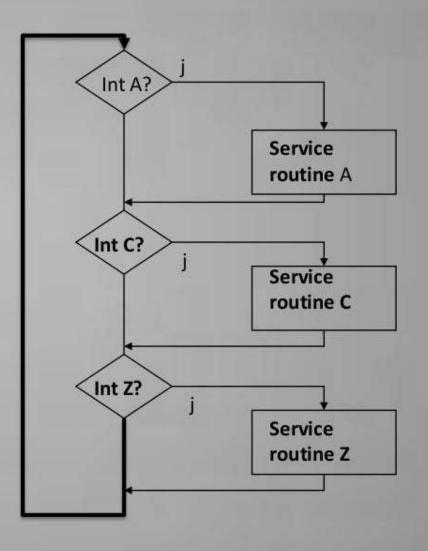

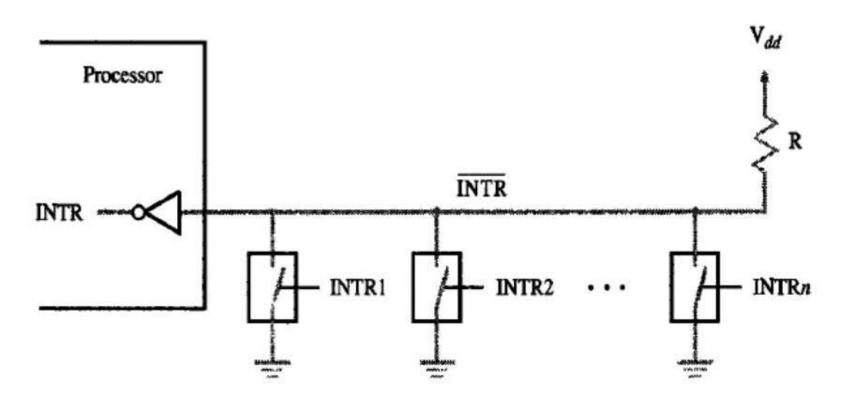

# 1.Enabling and disabling interrupts

- A processor has the facility to enable and disable interrupts as desired.

- When a device request the interrupt during the processor service for another interrupt, the result cause the processor enter into the infinite loop.

- This can be handled by the following 2 ways:

- The processor ignore the interrupt request line(INTR) until the Interrupt Service Routine(ISR) is completed.

- This can be done by using interrupt-Disable as first instruction and interrupt-Enable as the last instruction.

- The second option is processor automatically disable interrupts before starting the execution of the ISR.

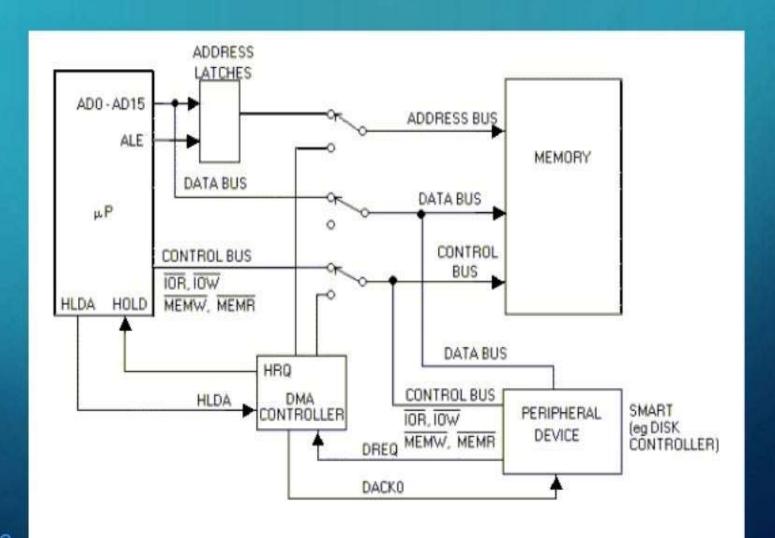

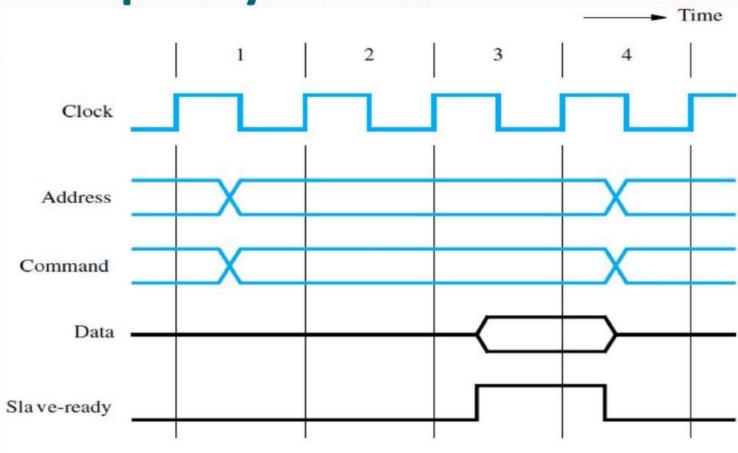

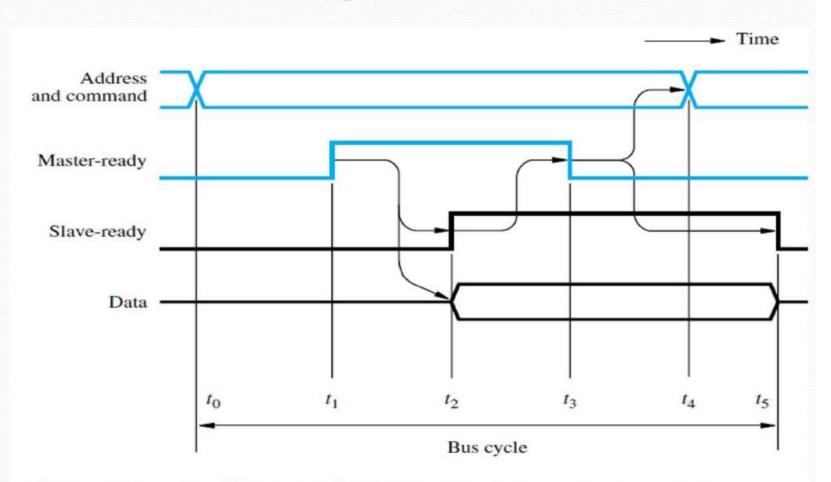

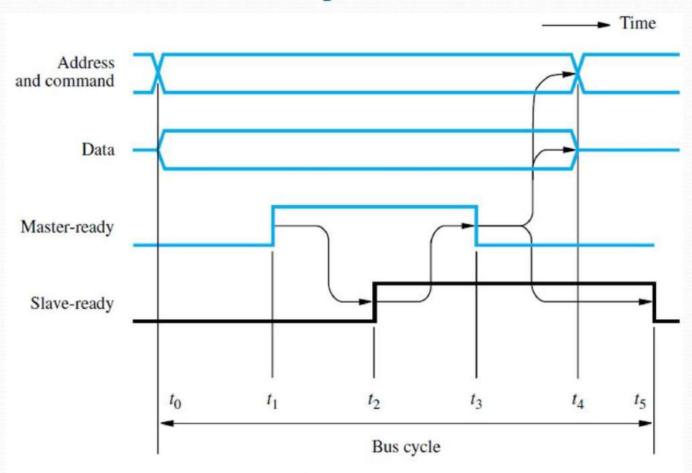

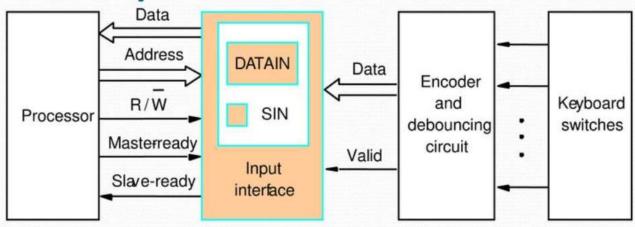

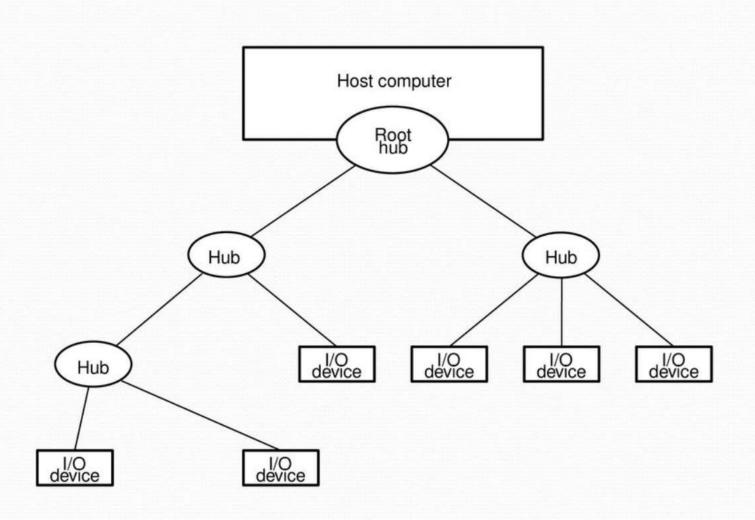

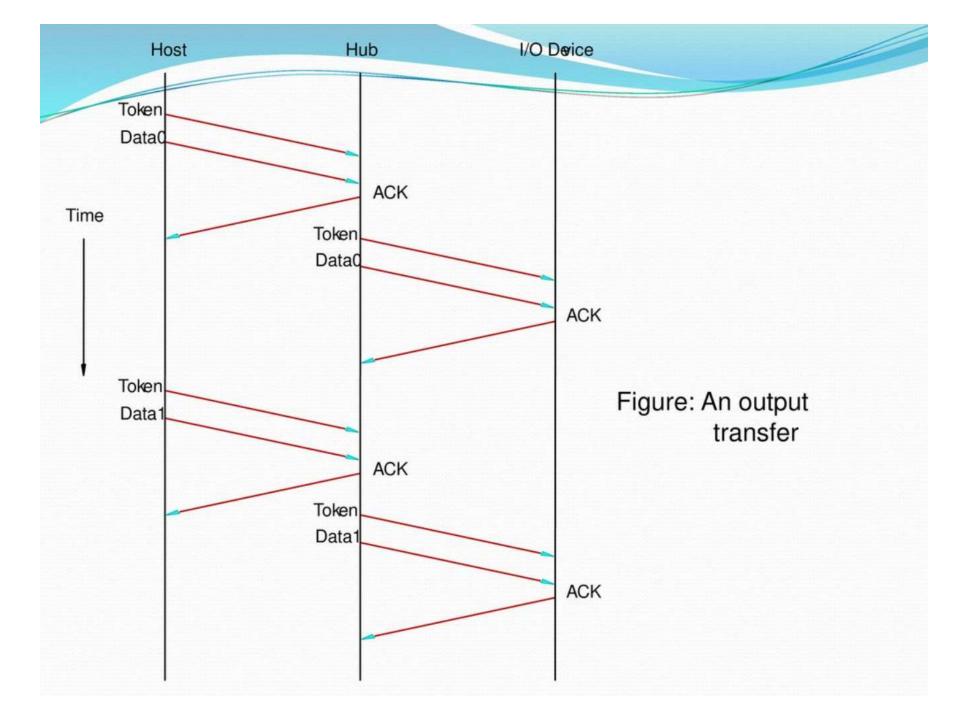

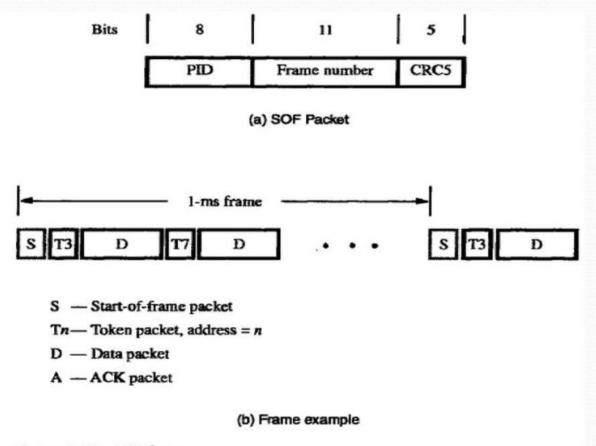

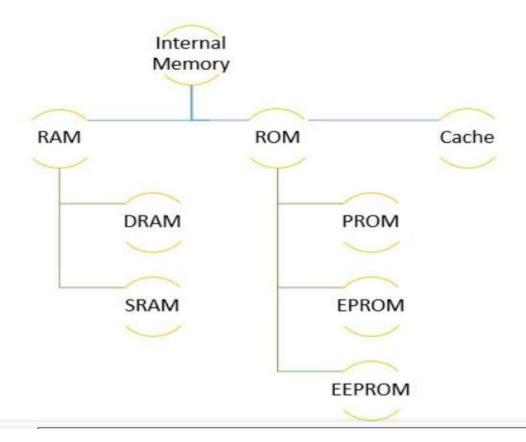

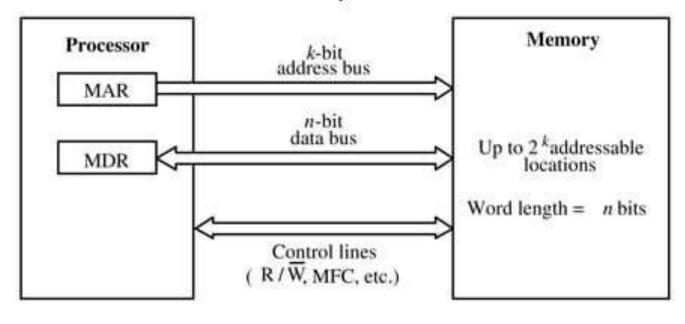

- The status register PS stored in the stack with PC value.